#### **ADVANCE** INFORMATION

June 1, 2010

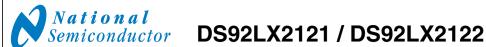

## 10 - 50 MHz Channel Link III Serializer and Deserializer with **Embedded Bi-Directional Control Channel**

#### **General Description**

The DS92LX2121/DS92LX2122 chipset offers a Channel Link III interface to deliver clock, high-speed data and a lowspeed, bidirectional I2C control bus over a single twisted wire pair. This single serial stream simplifies transferring a wide data bus over PCB traces and cable by eliminating clock to data skew, while reducing cable width and connector size. The DS92LX2121/DS92LX2122 incorporates differential signaling on both the high-speed and bi-directional back channel control data paths.

The Serializer/ Deserializer pair is ideally suited for driving video data with up to 18-bit color depth (RGB666 + HS, VS, and DE) along with a bi-directional back channel control bus. In addition, the Deserializer provides input equalization to compensate for loss from the media over longer distances. Internal DC balanced encoding/decoding is used to support AC-Coupled interconnects. Deserializer features such as output slew rate control, spread spectrum clock generation and staggered outputs can be enabled to lower EMI.

A sleep function provides a power-savings mode when the high speed forward channel and embedded bi-directional control channel are not needed.

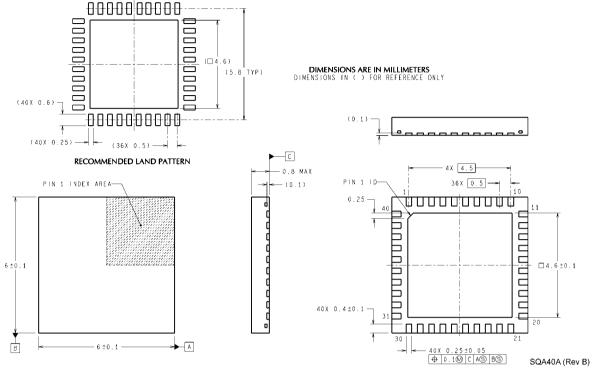

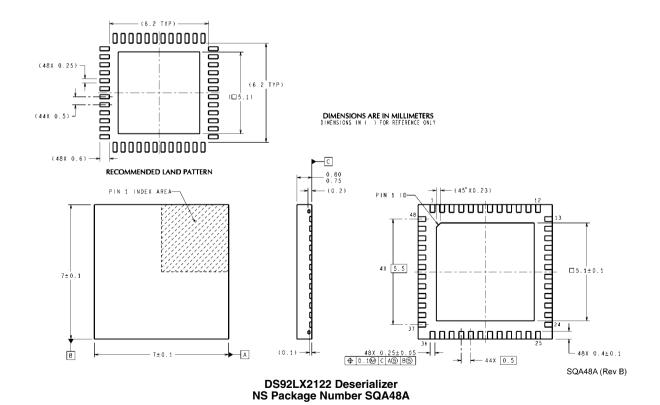

The Serializer is offered in a 40-pin lead in LLP and Deserializer is offered in a 48-pin LLP packages.

#### **Features**

- Up to 1050 Mbits/sec data throughput

- 10 MHz to 50 MHz input clock support

- Supports 18-bit color depth (RGB666 + HS, VS, DE)

- Embedded clock with DC Balanced coding to support ACcoupled interconnects

- Capable to drive up to 10 meters shielded twisted-pair

- Bi-directional control interface channel with I2C support

- I<sup>2</sup>C interface for device configuration. Single-pin ID addressing

- Up to 4 GPI on DES and GPO on SER

- AT-SPEED BIST diagnosis feature to validate link integrity

- Individual power-down controls for both SER and DES

- User-selectable clock edge for parallel data on both SER and DES

- Integrated termination resistors

- 1.8V- or 3.3V-compatible parallel bus interface

- Single power supply at 1.8V

- IEC 61000-4-2 ESD compliant

- Temperature range -40°C to +85°C

- No reference clock required on Deserializer

- Programmable Receive Equalization

- LOCK output reporting pin to ensure

- **EMI/EMC Mitigation**

- DES Programmable Spread Spectrum (SSCG) outputs

- DES Receiver Output clock and data slew rate select

- DES Receiver staggered outputs

#### **Applications**

- Industrial Displays, Touch Screens

- Medical Imaging

### **Typical Application Diagram**

30125127

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

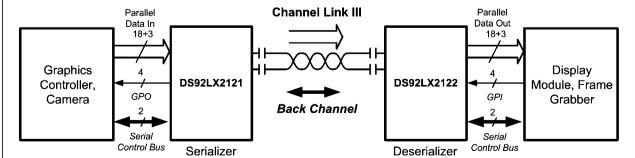

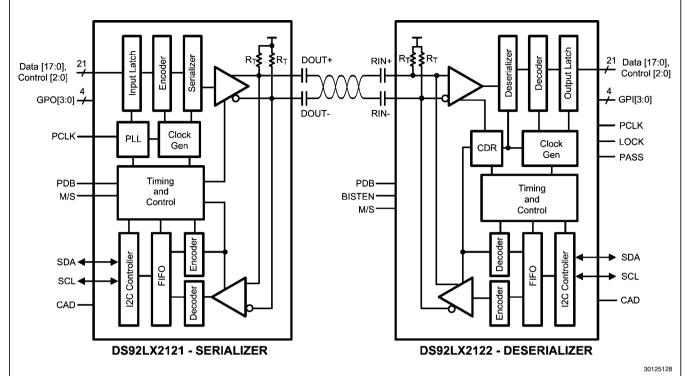

## **Block Diagrams**

FIGURE 1. Block Diagram

FIGURE 2. Application Block Diagram

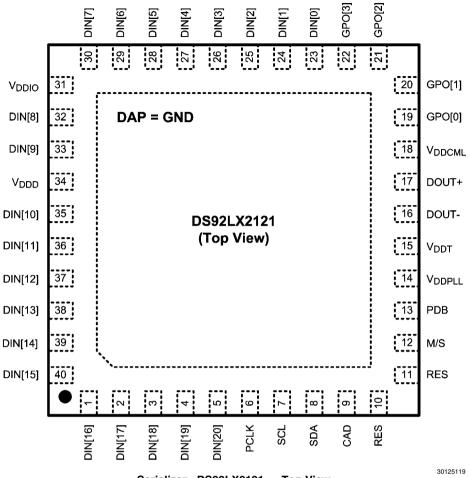

#### **DS92LX2121 Pin Diagram**

Serializer - DS92LX2121 — Top View

# **DS92LX2121 Serializer Pin Descriptions**

| Pin Name                  | Number of Pins   | I/O, Type                     | Description                                                                                                                           |  |  |  |  |  |

|---------------------------|------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| LVCMOS PARALLEL INTERFACE |                  |                               |                                                                                                                                       |  |  |  |  |  |

| DIN[20:0]                 | 21               | Inputs, LVCMOS w/             | Parallel data inputs.                                                                                                                 |  |  |  |  |  |

|                           |                  | pull down                     |                                                                                                                                       |  |  |  |  |  |

| PCLK                      | 1                | Input, LVCMOS w/              | Pixel Clock Input Pin. Strobe edge set by TRFB configuration.                                                                         |  |  |  |  |  |

|                           |                  | pull down                     |                                                                                                                                       |  |  |  |  |  |

| GENERAL PU                | RPOSE OUTPUT (   | GPO)                          |                                                                                                                                       |  |  |  |  |  |

| GPO[3:0]                  | 4                | Output, Digital               | General-purpose pins individually configured as outputs; which are used to                                                            |  |  |  |  |  |

|                           |                  |                               | control and respond to various commands.                                                                                              |  |  |  |  |  |

| SERIAL CONT               | ROL BUS - I2C CO | MPATIBLE                      |                                                                                                                                       |  |  |  |  |  |

| SCL                       | 1                | Input/Output, Open            | Clock line for the serial control bus communication                                                                                   |  |  |  |  |  |

|                           | '                | Drain                         | SCL requires an external pull-up resistor to V <sub>DDIO</sub> .                                                                      |  |  |  |  |  |

| SDA                       | 1                | Input/Output, Open            | Data line for the serial control bus communication                                                                                    |  |  |  |  |  |

|                           | '                | Drain                         | SDA requires an external pull-up resistor to V <sub>DDIO</sub> .                                                                      |  |  |  |  |  |

|                           |                  | Input, LVCMOS w/<br>pull down | I <sup>2</sup> C Master / Slave select                                                                                                |  |  |  |  |  |

| M/S                       | 1                |                               | M/S = L, Master (default)r; device generates and drives the SCL clock line                                                            |  |  |  |  |  |

|                           |                  |                               | M/S = H, Slave; device accepts SCL clock input                                                                                        |  |  |  |  |  |

|                           | 1                | Input, analog                 | Continuous Address Decoder                                                                                                            |  |  |  |  |  |

| CAD                       |                  |                               | Input pin to select the Slave Device Address.                                                                                         |  |  |  |  |  |

|                           |                  |                               | Input is connect to external resistor divider to programmable Device ID                                                               |  |  |  |  |  |

| OONTROL AND               | ID CONTINUE ATIO |                               | address (see Serial Control Bus Connection).                                                                                          |  |  |  |  |  |

| CONTROL AN                | ID CONFIGURATIO  | N                             | I                                                                                                                                     |  |  |  |  |  |

|                           |                  | Input, LVCMOS w/<br>pull down | Power down Mode Input Pin.                                                                                                            |  |  |  |  |  |

| PDB                       | 1                |                               | PDB = H, Transmitter is enabled and is ON.                                                                                            |  |  |  |  |  |

|                           |                  |                               | PDB = L, Transmitter is in Sleep (Power Down). When the transmitter is in the SLEEP state, the PLL is shutdown, and IDD is minimized. |  |  |  |  |  |

|                           |                  | Input, LVCMOS w/              | Reserved. This pin MUST be tied LOW.                                                                                                  |  |  |  |  |  |

| RES                       | 2                | pull down                     | These ved. This pill wost be tied Low.                                                                                                |  |  |  |  |  |

| Channel Link              | III INTERFACE    | pa do                         |                                                                                                                                       |  |  |  |  |  |

| DOUT+                     | 1                | Input/Output, CML             | Non-inverting differential output, back-channel input.                                                                                |  |  |  |  |  |

| DOUT-                     | 1                | Input/Output, CML             | Inverting differential output, back-channel input.                                                                                    |  |  |  |  |  |

| Power and Gro             | -                | mpar output, omi              | Involving amore man output, back original input.                                                                                      |  |  |  |  |  |

| VDDPLL                    | 1                | Power, Analog                 | PLL Power, 1.8V ±5%                                                                                                                   |  |  |  |  |  |

| VDDT                      | 1                | Power, Analog                 | ·                                                                                                                                     |  |  |  |  |  |

| VDDCML                    | 1                | Power, Analog Power, Analog   | Tx Analog Power, 1.8V ±5%                                                                                                             |  |  |  |  |  |

|                           |                  | · · ·                         | LVDS & BC Dr Power, 1.8V ±5%                                                                                                          |  |  |  |  |  |

| VDDD                      | 1                | Power, Digital                | Digital Power, 1.8V ±5%                                                                                                               |  |  |  |  |  |

| VDDIO                     | 1                | Power, Digital                | Power for input stage, The single-ended inputs are powered from V <sub>DDIO</sub> .                                                   |  |  |  |  |  |

| VSS                       | -                | Ground, DAP                   | All VSS pads are down bonded to DAP. DAP must be grounded.                                                                            |  |  |  |  |  |

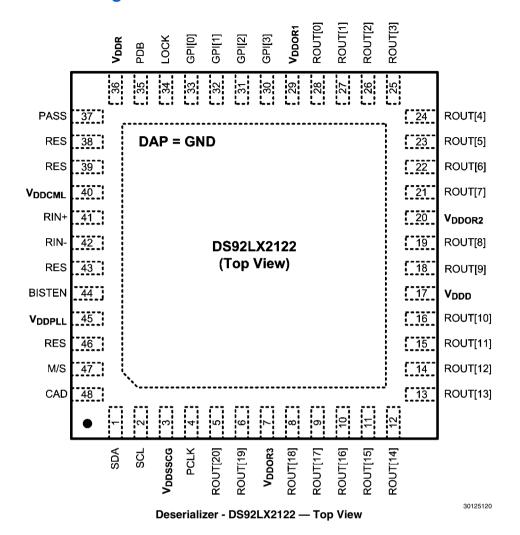

#### **DS92LX2122 Pin Diagram**

5

# **DS92LX2122 Deserializer Pin Descriptions**

| Pin Name                    | Number of Pins   | I/O, Type                     | Description                                                                                                        |  |  |  |  |

|-----------------------------|------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| LVCMOS PARALLEL INTERFACE   |                  |                               |                                                                                                                    |  |  |  |  |

| ROUT[20:0]                  | 21               | Outputs, LVCMOS               | Parallel data outputs.                                                                                             |  |  |  |  |

|                             |                  |                               | Pixel Clock Output Pin.                                                                                            |  |  |  |  |

| PCLK                        | 1                | Output, LVCMOS                | Strobe edge set by RFB configuration. In SLEEP, outputs are controlled by the OSS_SEL.                             |  |  |  |  |

| General Purpose Input (GPI) |                  |                               |                                                                                                                    |  |  |  |  |

| GPI[3:0] 4 Input/Output, D  |                  | Input/Output, Digital         | General-purpose pins individually configured as inputs; which are used to control and respond to various commands. |  |  |  |  |

| SERIAL CONT                 | ROL BUS - I2C CO | MPATIBLE                      |                                                                                                                    |  |  |  |  |

| 201                         | _                | Input/Output, Open            | Clock line for the serial control bus communication                                                                |  |  |  |  |

| SCL                         | 1                | Drain                         | SCL requires an external pull-up resistor to V <sub>DDIO</sub> .                                                   |  |  |  |  |

| OD A                        |                  | Input/Output, Open            | Data line for serial control bus communication                                                                     |  |  |  |  |

| SDA                         | 1                | Drain                         | SDA requires an external pull-up resistor to V <sub>DDIO</sub> .                                                   |  |  |  |  |

|                             |                  | Input, LVCMOS w/              | I <sup>2</sup> C Master / Slave select                                                                             |  |  |  |  |

| M/S                         | 1                |                               | M/S = L, Master; device generates and drives the SCL clock line                                                    |  |  |  |  |

|                             |                  |                               | M/S = H, Slave (default); device accepts SCL clock input                                                           |  |  |  |  |

|                             |                  | Input, analog                 | Continuous Address Decoder                                                                                         |  |  |  |  |

| CAD                         |                  |                               | Input pin to select the Slave Device Address.                                                                      |  |  |  |  |

| CAD                         | 1                |                               | Input is connect to external resistor divider to programmable Device ID                                            |  |  |  |  |

|                             |                  |                               | address (see Serial Control Bus Connection)                                                                        |  |  |  |  |

| CONTROL AN                  | ID CONFIGURATION | N                             |                                                                                                                    |  |  |  |  |

|                             | 1                | Input, LVCMOS w/<br>pull down | Power down Mode Input Pin.                                                                                         |  |  |  |  |

|                             |                  |                               | PDB = H, Receiver is enabled and is ON.                                                                            |  |  |  |  |

| PDB                         |                  |                               | PDB = L, Receiver is in Sleep (Power down mode). When the Receiver is in                                           |  |  |  |  |

|                             |                  |                               | the SLEEP state, the LVCMOS Outputs are in TRI-STATE, the PLL is                                                   |  |  |  |  |

|                             |                  |                               | shutdown and IDD is minimized.                                                                                     |  |  |  |  |

|                             | 1                | Output, LVCMOS                | LOCK Status Output Pin.                                                                                            |  |  |  |  |

| LOCK                        |                  |                               | LOCK = H, PLL is Locked, outputs are active                                                                        |  |  |  |  |

| LOCK                        |                  |                               | LOCK = L, PLL is unlocked, ROUT and PCLK output states are controlled by                                           |  |  |  |  |

|                             |                  |                               | OSS_SEL. May be used as Link Status.                                                                               |  |  |  |  |

|                             | 4                | -                             | Reserved.                                                                                                          |  |  |  |  |

| RES                         |                  |                               | Pin 46: This pin MUST be tied LOW.                                                                                 |  |  |  |  |

|                             |                  |                               | Pins 38, 39, 43: Leave pin open.                                                                                   |  |  |  |  |

| BIST MODE                   |                  |                               |                                                                                                                    |  |  |  |  |

|                             | 1                | Input I VCMOS ···/            | BIST Enable Pin.                                                                                                   |  |  |  |  |

| BISTEN                      |                  | Input, LVCMOS w/<br>pull down | BISTEN = H, BIST Mode is enabled.                                                                                  |  |  |  |  |

|                             |                  |                               | BISTEN = L, BIST Mode is disabled.                                                                                 |  |  |  |  |

| PASS                        | 1                | Output, LVCOMS                | PASS Output Pin for BIST mode.                                                                                     |  |  |  |  |

|                             |                  |                               | PASS = H, ERROR FREE Transmission                                                                                  |  |  |  |  |

|                             |                  |                               | PASS = L, one or more errors were detected in the received payload.                                                |  |  |  |  |

|                             |                  |                               | Leave Open if unused. Route to test point (pad) recommended.                                                       |  |  |  |  |

| Channel Link                | III INTERFACE    |                               |                                                                                                                    |  |  |  |  |

| RIN+                        | 1                | Input/Output, CML             | Noninverting differential input, back channel output.                                                              |  |  |  |  |

| RIN-                        | 1                | Input/Output, CML             | Inverting differential input, back channel output.                                                                 |  |  |  |  |

|                             | <u>.</u>         |                               | 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                            |  |  |  |  |

| Pin Name         | Number of Pins | I/O, Type     | Description                                                                                                                                              |  |  |  |  |

|------------------|----------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| POWER AND GROUND |                |               |                                                                                                                                                          |  |  |  |  |

| VDDSSCG          | 1              | Digital Power | SSCG Power, 1.8V ±5%                                                                                                                                     |  |  |  |  |

| VDDOR1/2/3       | 3              | Digital Power | TTL Output Buffer Power, The single-ended outputs and control input are powered from $V_{DDIO}$ . $V_{DDIO}$ can be connected to a 1.8V ±5% or 3.3V ±10% |  |  |  |  |

| VDDD             | 1              | Digital Power | Digital Core Power, 1.8V ±5%                                                                                                                             |  |  |  |  |

| VDDR             | 1              | Analog Power  | Rx Analog Power, 1.8V ±5%                                                                                                                                |  |  |  |  |

| VDDCML           | 1              | Analog Power  | BC Driver Power, 1.8V ±5%                                                                                                                                |  |  |  |  |

| VDDPLL           | 1              | Analog Power  | PLL Power, 1.8V ±5%                                                                                                                                      |  |  |  |  |

| VSS              | -              | Ground        | All VSS pads are down bonded to DAP. DAP must be grounded.                                                                                               |  |  |  |  |

#### Physical Dimensions inches (millimeters) unless otherwise noted

DS92LX2121 Serializer

NS Package Number SQA40A

#### **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at: www.national.com

| Pr                             | oducts                       | Design Support                  |                                |  |

|--------------------------------|------------------------------|---------------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools                  | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | App Notes                       | www.national.com/appnotes      |  |

| Clock and Timing               | www.national.com/timing      | Reference Designs               | www.national.com/refdesigns    |  |

| Data Converters                | www.national.com/adc         | Samples                         | www.national.com/samples       |  |

| Interface                      | www.national.com/interface   | Eval Boards                     | www.national.com/evalboards    |  |

| LVDS                           | www.national.com/lvds        | Packaging                       | www.national.com/packaging     |  |

| Power Management               | www.national.com/power       | Green Compliance                | www.national.com/quality/green |  |

| Switching Regulators           | www.national.com/switchers   | Distributors                    | www.national.com/contacts      |  |

| LDOs                           | www.national.com/ldo         | Quality and Reliability         | www.national.com/quality       |  |

| LED Lighting                   | www.national.com/led         | Feedback/Support                | www.national.com/feedback      |  |

| Voltage References             | www.national.com/vref        | Design Made Easy                | www.national.com/easy          |  |

| PowerWise® Solutions           | www.national.com/powerwise   | Applications & Markets          | www.national.com/solutions     |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                        | www.national.com/milaero       |  |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                     | www.national.com/solarmagic    |  |

| PLL/VCO                        | www.national.com/wireless    | PowerWise® Design<br>University | www.national.com/training      |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2010 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com