Buy

#### TPS65720, TPS657201, TPS657202, TPS65721

SLVS979B-OCTOBER 2009-REVISED OCTOBER 2016

# TPS6572x Integrated PMIC With 1 DC-DC, 1 LDO, Battery Charger and GPIO

#### 1 Features

Texas

INSTRUMENTS

- Battery Charger With Power Path Management

- 28-V Rated Power Path With:

- 100-mA Input Current Limit

- 500-mA Input Current Limit

- 300-mA Charge Current

- 200-mA Step-Down Converter for TPS65720

- 400-mA Step-Down Converter for TPS65721, TPS657201, TPS657202

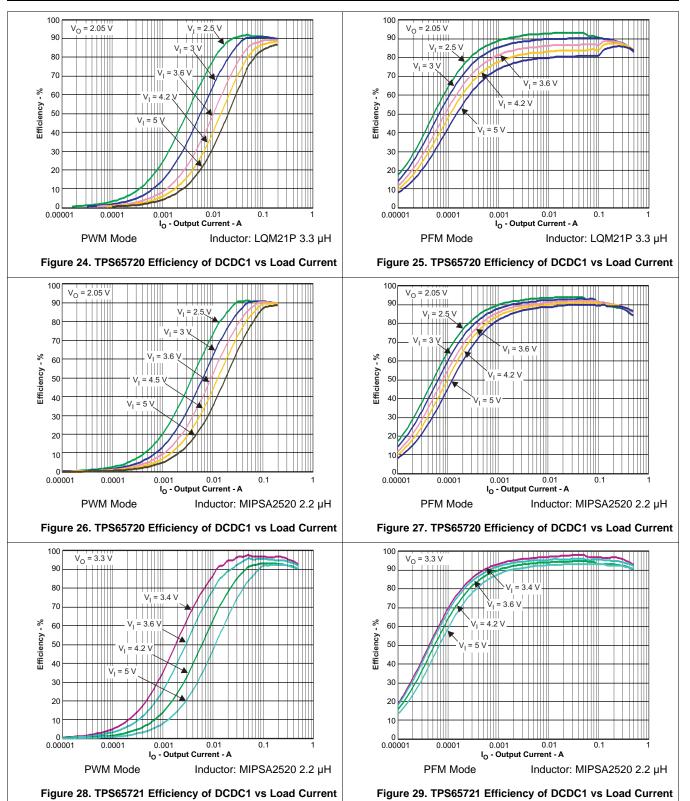

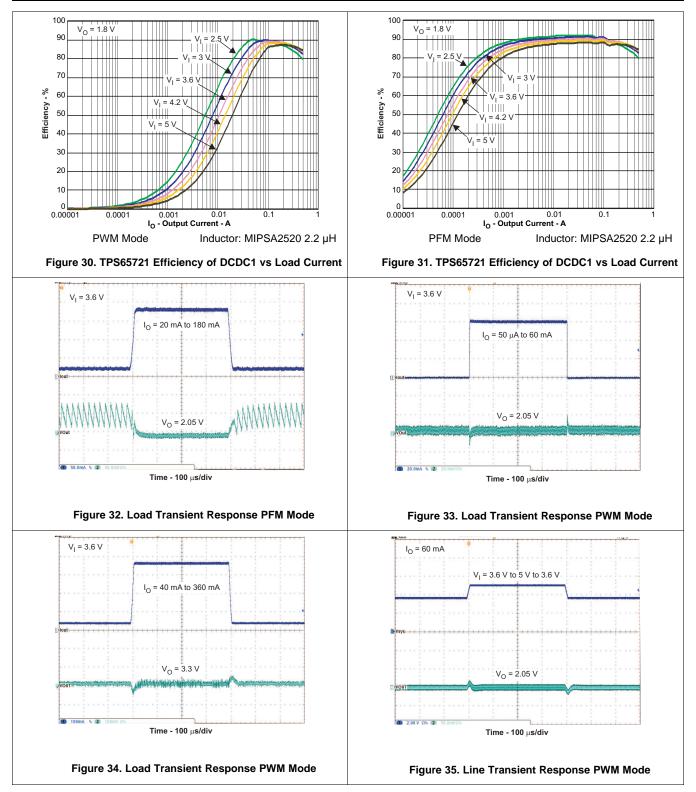

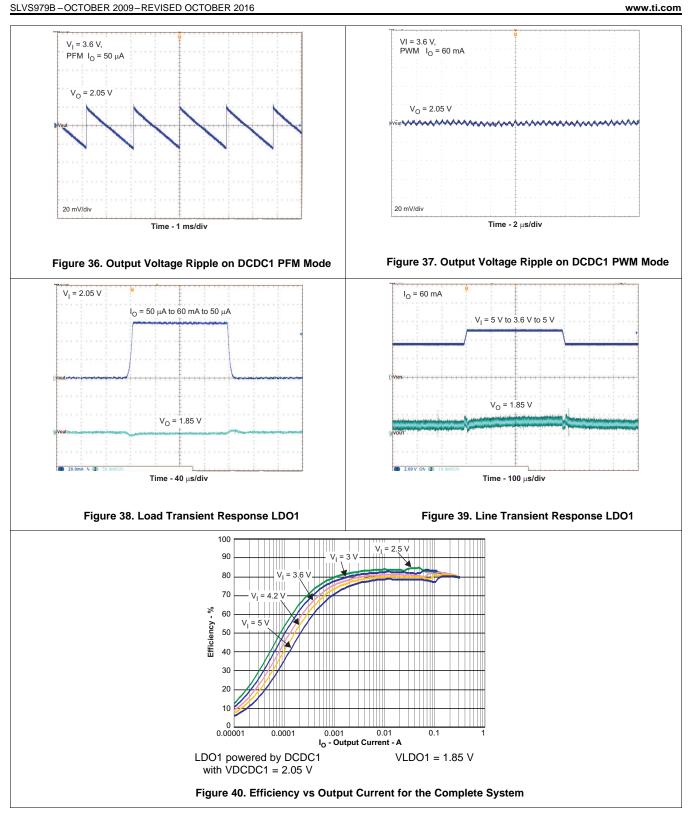

- Up to 92% Efficiency

- V<sub>IN</sub> Range for DCDC Converter From 2.3 V to • 5.6 V

- 2.25-MHz Fixed Frequency Operation

- Power Save Mode at Light Load Current

- Output Voltage Accuracy in PWM Mode ±2%

- 100% Duty Cycle for Lowest Dropout

- 1 General Purpose 200-mA LDO

- V<sub>IN</sub> Range for LDO From 1.8 V to 5.6 V

- I<sup>2</sup>C Compatible Interface

- 4GPIOs

- Available in a 25-Ball DSBGA With 0.4-mm Pitch and in 4-mm × 4-mm 32-Pin WQFN Package

# 2 Applications

- **Bluetooth Headsets**

- Handheld Equipment

- Wearables, Smart Watches

- Portable Accessories

#### Description 3

The TPS6572x device is a small power management unit targeted for Bluetooth headsets or other portable low-power consumer-end equipments. The device contains an USB friendly Lithium-Ion battery charger, a highly efficient step-down converter, a low-dropout linear regulator, and additional supporting functions. The device is controlled by an I<sup>2</sup>C interface. Several settings can be customized by the use of nonvolatile memory which is factory programmed.

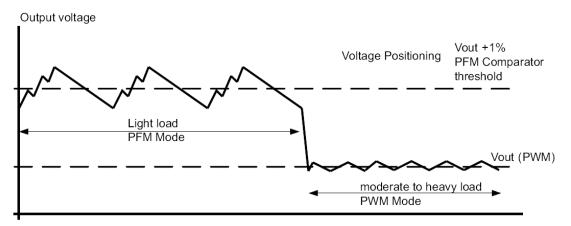

The 2.25-MHz step-down converter enters a lowpower mode at light load for maximum efficiency across the widest possible range of load currents. For low-noise applications the devices can be forced into fixed-frequency PWM mode using the I<sup>2</sup>C-compatible interface.

The device allows the use of small inductors and capacitors to achieve a small solution size. The TPS65720 provides an output current of up to

200 mA on the DC-DC converter while TPS657201, TPS657202, and TPS65721 provide up to 400 mA. The TPS6572x also integrates one 200-mA LDO. The LDO operates with an input voltage range from 1.8 V to 5.6 V, thus allowing it to be supplied from the output of the step-down converter or directly from the system voltage.

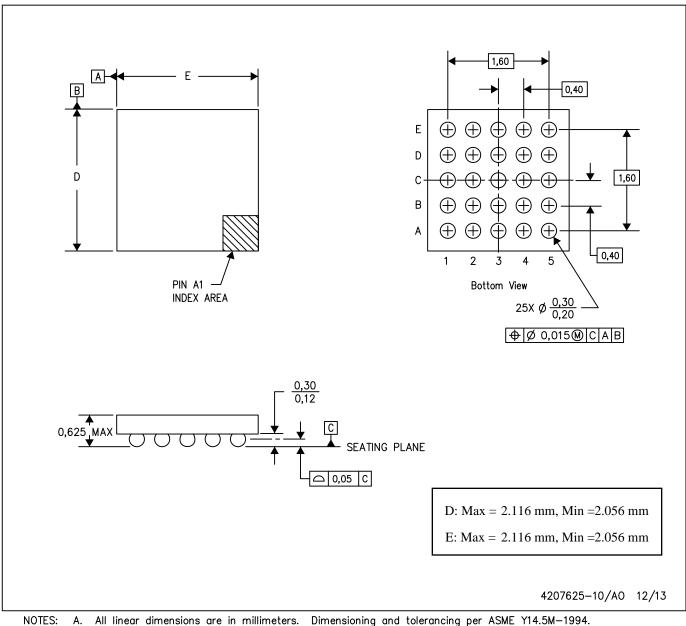

The TPS65720, TPS657201, and TPS657202 come in a small 25-ball 2-mm × 2-mm wafer chip scale package (DSBGA) with 0.4-mm ball pitch or a 4-mm × 4-mm WQFN package with a 0.4-mm pitch (TPS65721).

#### Device Information <sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| TPS65720x   | DSBGA (25) | 2.11 mm × 2.11 mm |

| TPS65721    | WQFN (32)  | 4.00 mm × 4.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

Product Folder Links: TPS65720 TPS657201 TPS657202 TPS65721

# **Table of Contents**

| 1 | Feat | tures 1                          |

|---|------|----------------------------------|

| 2 | Арр  | lications 1                      |

| 3 |      | cription 1                       |

| 4 | Rev  | ision History 2                  |

| 5 | Dev  | ice Options                      |

| 6 |      | Configuration and Functions 4    |

| 7 | Spe  | cifications7                     |

|   | 7.1  | Absolute Maximum Ratings 7       |

|   | 7.2  | ESD Ratings7                     |

|   | 7.3  | Recommended Operating Conditions |

|   | 7.4  | Thermal Information 8            |

|   | 7.5  | Electrical Characteristics8      |

|   | 7.6  | Dissipation Ratings 14           |

|   | 7.7  | Timing Requirements 14           |

|   | 7.8  | Switching Characteristics 15     |

|   | 7.9  | Typical Characteristics 16       |

| 8 | Deta | ailed Description 18             |

|   | 8.1  | Overview 18                      |

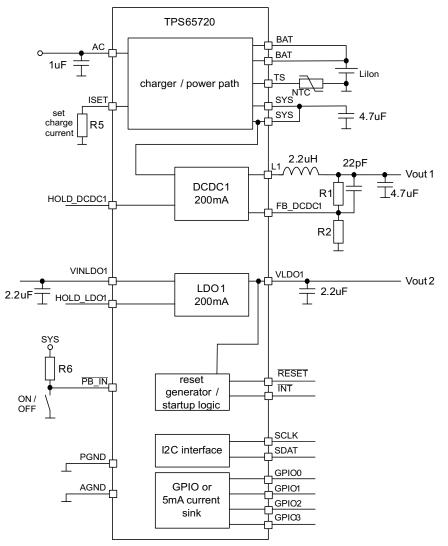

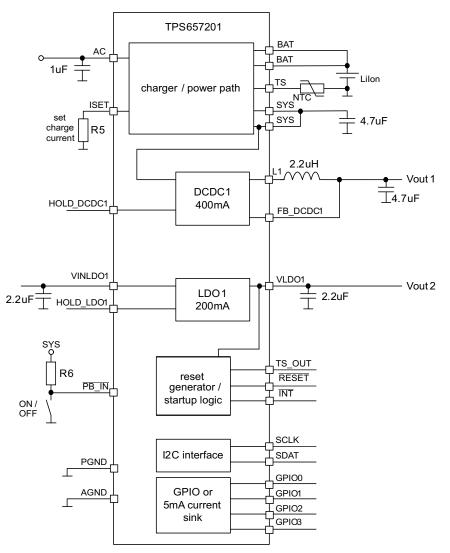

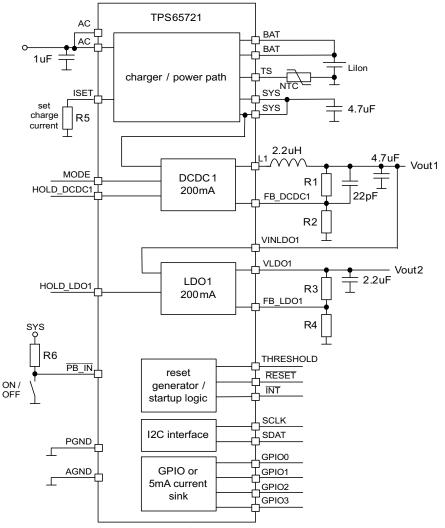

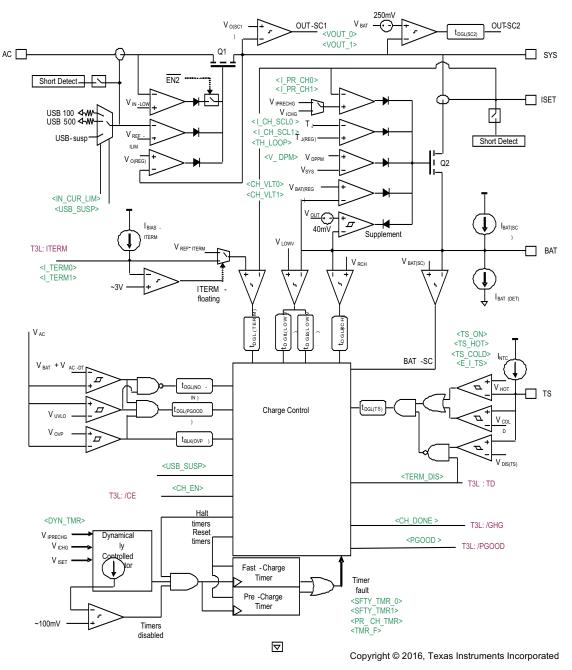

|   | 8.2  | Functional Block Diagrams 18     |

|   | 8.3  | Feature Description 20           |

|   |      |                                  |

|    | 8.4  | Device Functional Modes                         | 30 |

|----|------|-------------------------------------------------|----|

|    | 8.5  | Programming                                     | 31 |

|    | 8.6  | Register Maps                                   | 33 |

| 9  | Арр  | lication and Implementation                     | 46 |

|    | 9.1  | Application Information                         | 46 |

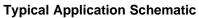

|    | 9.2  | Typical Application                             | 46 |

| 10 | Pow  | ver Supply Recommendations                      | 55 |

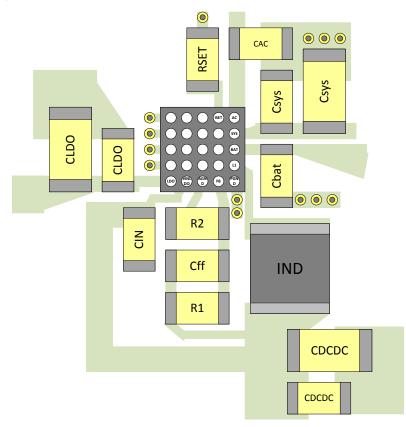

| 11 | Lay  | out                                             | 55 |

|    | 11.1 | Layout Guidelines                               | 55 |

|    | 11.2 | Layout Example                                  | 55 |

| 12 | Dev  | ice and Documentation Support                   | 56 |

|    | 12.1 | Device Support                                  | 56 |

|    | 12.2 | Documentation Support                           | 56 |

|    | 12.3 | Related Links                                   | 56 |

|    | 12.4 | Receiving Notification of Documentation Updates | 56 |

|    | 12.5 |                                                 |    |

|    | 12.6 |                                                 |    |

|    | 12.7 |                                                 |    |

|    | 12.8 | Glossary                                        | 57 |

| 13 | Mec  | hanical, Packaging, and Orderable               |    |

|    | Info | mation                                          | 57 |

|    |      |                                                 |    |

# **4** Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Revision A (September 2015) to Revision B

| • | Changed <i>Timer Fault</i> , To: Charger Fault, and Bit <timer_fault> = 1 To: Bit <ch_fault> = 1</ch_fault></timer_fault> | 24 |

|---|---------------------------------------------------------------------------------------------------------------------------|----|

| • | IRMASKO Register Address: 0Dh (read/write), Changed B4 From: M_TIMER_FAULT To: Reserved                                   | 43 |

| • | IRO Register Address: 10h (read only), Changed B4 From: TIMER_FAULT To: Reserved                                          | 44 |

|   | 100 Perioter Address 40k (read ank), Changed D4 From Dising adre of TIMED, FAULT To: Described                            |    |

#### Changes from Original (October 2009) to Revision A

| • | Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and |   |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|   | Mechanical, Packaging, and Orderable Information section                                                                                                                                                                   | 1 |

| • | Added the TPS657202 and the TPS65721 devices to the data sheet                                                                                                                                                             | 1 |

2

www.ti.com

#### Page

Page

# **5** Device Options

| PART NUMBER <sup>(1)</sup> | SIZE FOR DSBGA PACKAGE                   | OPTION                                                                                                        |

|----------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| TPS65720                   | D = 2105 μm ±25 μm<br>E = 2105 μm ±25 μm | DCDC1 externally adjustable<br>LDO1 default 1.85 V<br>AC input current limit = 500 mA                         |

| TPS657201                  | D = 2105 μm ±25 μm<br>E = 2105 μm ±25 μm | DCDC1 default 1.85 V<br>LDO1 default 1.85 V<br>analog multiplexer (TS_OUT)<br>AC input current limit = 500 mA |

| TPS657202                  | D = 2105 μm ±25 μm<br>E = 2105 μm ±25 μm | DCDC1 default 1.90 V<br>LDO1 default 2.85 V<br>analog multiplexer (TS_OUT)<br>AC input current limit = 100 mA |

| TPS65721                   | _                                        | DCDC1 externally adjustable<br>LDO1 externally adjustable<br>AC input current limit = 500 mA                  |

(1) The RSN and YFF package is available in tape and reel. Add R suffix (TPS65720YFFR; TPS65721RSNR) to order quantities of 3000 parts per reel. Add T suffix (TPS65720YFFT; TPS65721RSNT) to order quantities of 250 parts per reel.

#### Texas Instruments

www.ti.com

# 6 Pin Configuration and Functions

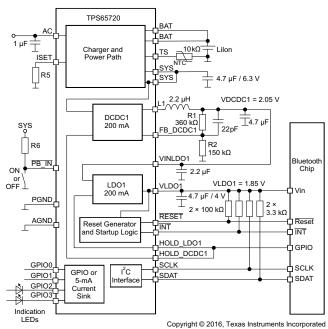

## Pin Functions—DSBGA (TPS65720)

| PIN |            |     |                                                                                                                                      |  |

|-----|------------|-----|--------------------------------------------------------------------------------------------------------------------------------------|--|

| NO. | NAME       | I/O | DESCRIPTION                                                                                                                          |  |

| A1  | VLDO1      | 0   | Output voltage of LDO1                                                                                                               |  |

| A2  | HOLD_LDO1  | I   | Power-on input for LDO1. When pulled HIGH, LDO1 is kept enabled after PB_IN was released HIGH.                                       |  |

| A3  | GPIO3      | I/O | General purpose I/O or 5-mA current sink                                                                                             |  |

| A4  | GPIO1      | I/O | General purpose I/O                                                                                                                  |  |

| A5  | SCLK       | I   | Clock input for the I <sup>2</sup> C interface                                                                                       |  |

| B1  | VINLDO1    | I   | Input voltage for LDO1                                                                                                               |  |

| B2  | GND        | _   | Connect to AGND and PGND                                                                                                             |  |

| B3  | GPIO2      | I/O | General purpose I/O or 5-mA current sink                                                                                             |  |

| B4  | GPIO0      | I/O | General purpose I/O                                                                                                                  |  |

| B5  | SDAT       | I/O | Data line for the I <sup>2</sup> C interface                                                                                         |  |

| C1  | AGND       | _   | Analog ground                                                                                                                        |  |

| C2  | TS         | I   | nect a thermistor from this pin to GND for battery temperature                                                                       |  |

| C3  | INT        | 0   | n-drain interrupt output                                                                                                             |  |

| C4  | PB_IN      | I.  | h button input; Turns on DCDC1 and LDO1 if pulled to GND.                                                                            |  |

| C5  | RESET      | 0   | ben-drain output of the reset generator; This output goes active LOW when the output voltage of LDO1 falls 8% below its target tage. |  |

| D1  | FB_DCDC1   | I   | Feedback input of step-down converter                                                                                                |  |

| D2  | HOLD_DCDC1 | I   | Power-On input for DCDC1 converter. When pulled HIGH, the DC-DC converter is kept enabled after PB_IN was released HIGH.             |  |

| D3  | BAT        | I/O | Connect to battery + terminal                                                                                                        |  |

| D4  | SYS        | 0   | System voltage; output of the power path manager. Power input for step-down converter DCDC1                                          |  |

| D5  | ISET       | I.  | Connect a resistor from this pin to GND to set fast charge current                                                                   |  |

| E1  | PGND       | —   | Power ground                                                                                                                         |  |

| E2  | L1         | 0   | Switch output of step-down converter                                                                                                 |  |

| E3  | BAT        | I/O | Connect to battery + terminal                                                                                                        |  |

| E4  | SYS        | 0   | System voltage; output of the power path manager. Power input for step-down converter DCDC1                                          |  |

| E5  | AC         | I   | Input power for power manager, connect to external DC supply.                                                                        |  |

**TPS65720, TPS657201, TPS657202, TPS65721** SLVS979B – OCTOBER 2009 – REVISED OCTOBER 2016

www.ti.com

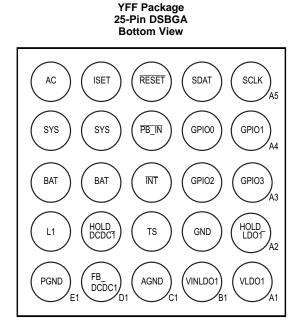

# Pin Functions—DSBGA (TPS657201, TPS657202)

| PIN |             | 1/0   |                                                                                                                                          |

|-----|-------------|-------|------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME        | - I/O | DESCRIPTION                                                                                                                              |

| A1  | VLDO1       | 0     | Output voltage of LDO1                                                                                                                   |

| A2  | HOLD_LDO1   | I     | Power-on input for LDO1. When pulled HIGH, LDO1 is kept enabled after PB_IN was released HIGH.                                           |

| A3  | GPIO3       | I/O   | General purpose I/O or 5-mA current sink                                                                                                 |

| A4  | GPIO1       | I/O   | General purpose I/O                                                                                                                      |

| A5  | SCLK        | I     | Clock input for the I <sup>2</sup> C interface                                                                                           |

| B1  | VINLDO1     | I     | Input voltage for LDO1                                                                                                                   |

| B2  | VBAT/TS_OUT | 0     | Output of battery temperature and battery voltage monitor                                                                                |

| B3  | GPIO2       | I/O   | General purpose I/O or 5-mA current sink                                                                                                 |

| B4  | GPIO0       | I/O   | General purpose I/O                                                                                                                      |

| B5  | SDAT        | I/O   | Data line for the I <sup>2</sup> C interface                                                                                             |

| C1  | AGND        | _     | Analog ground                                                                                                                            |

| C2  | TS          | I     | Connect a thermistor from this pin to GND for battery temperature                                                                        |

| C3  | INT         | 0     | Open-drain interrupt output                                                                                                              |

| C4  | PB_IN       | I     | Push button input; Turns on DCDC1 and LDO1 if pulled to GND.                                                                             |

| C5  | RESET       | 0     | Open-drain output of the reset generator; This output goes active LOW when the output voltage of LDO1 falls 8% below its target voltage. |

| D1  | FB_DCDC1    | I     | Feedback input of step-down converter                                                                                                    |

| D2  | HOLD_DCDC1  | I     | Power-on input for DCDC1 converter. When pulled HIGH, the DC-DC converter is kept enabled after PB_IN was released HIGH.                 |

| D3  | BAT         | I/O   | Connect to battery + terminal                                                                                                            |

| D4  | SYS         | 0     | System voltage; output of the power path manager. Power input for step-down converter DCDC1                                              |

| D5  | ISET        | I     | Connect a resistor from this pin to GND to set fast charge current                                                                       |

| E1  | PGND        | -     | Power ground                                                                                                                             |

| E2  | L1          | 0     | Switch output of step-down converter                                                                                                     |

| E3  | BAT         | I/O   | Connect to battery + terminal                                                                                                            |

| E4  | SYS         | 0     | System voltage; output of the power path manager. Power input for step-down converter DCDC1                                              |

| E5  | AC          | I     | Input power for power manager, connect to external DC supply.                                                                            |

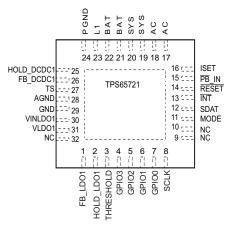

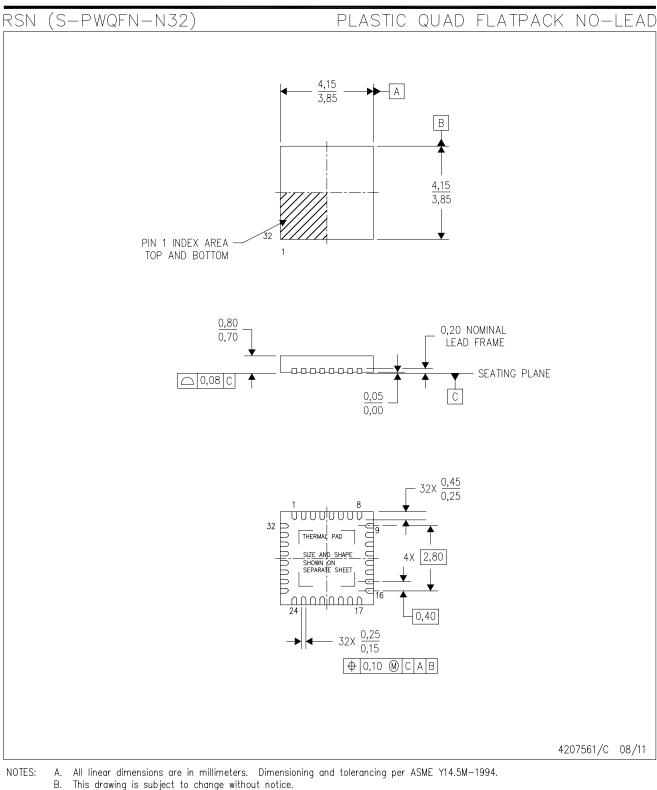

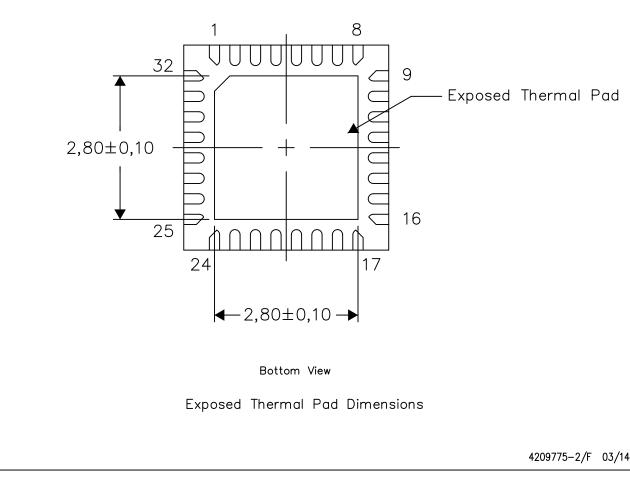

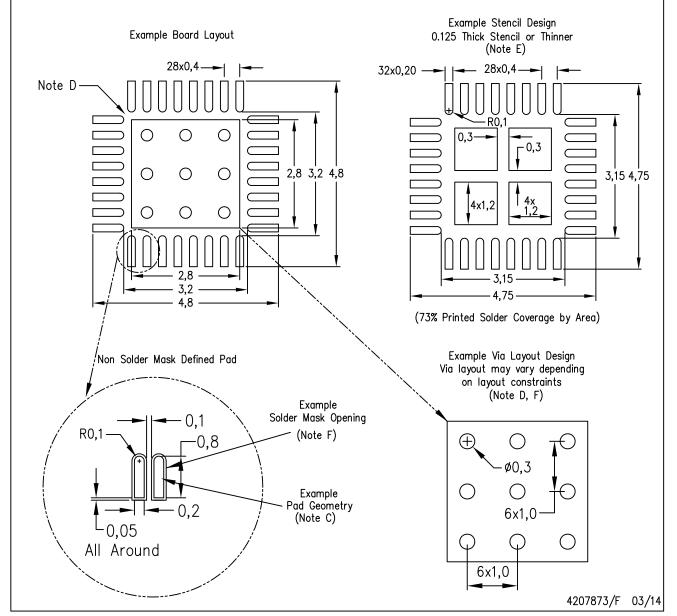

#### RSN Package 32-Pin WQFN With Thermal Pad Top View

# Pin Functions—WQFN (TPS65721)

| PIN        |        |     | DECODIDION                                                                                                                                       |  |

|------------|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME       | NO.    | I/O | DESCRIPTION                                                                                                                                      |  |

| AC         | 17, 18 | I   | Input power for power manager, connect to external DC supply.                                                                                    |  |

| AGND       | 28     | _   | Analog ground                                                                                                                                    |  |

| BAT        | 21, 22 | I/O | Connect to battery + terminal                                                                                                                    |  |

| FB_DCDC1   | 26     | I   | Feedback input of step-down converter                                                                                                            |  |

| FB_LDO1    | 1      | I   | Feedback input for LDO1                                                                                                                          |  |

| GND        | 29     | _   | onnect to AGND and PGND                                                                                                                          |  |

| GPIO0      | 7      | I/O | General purpose I/O                                                                                                                              |  |

| GPIO1      | 6      | I/O | General purpose I/O                                                                                                                              |  |

| GPIO2      | 5      | I/O | General purpose I/O or 5-mA current source                                                                                                       |  |

| GPIO3      | 4      | I/O | General purpose I/O or 5-mA current source                                                                                                       |  |

| HOLD_DCDC1 | 25     | I   | Power-on input for DCDC1 converter. When pulled HIGH, the DC-DC converter is kept enabled after PB_IN was released HIGH.                         |  |

| HOLD_LDO1  | 2      | I   | Power-on input for LDO1. When pulled HIGH, LDO1 is kept enabled after PB_IN was released HIGH.                                                   |  |

| INT        | 13     | 0   | Open-drain interrupt output                                                                                                                      |  |

| ISET       | 16     | I   | Connect a resistor from this pin to GND to set fast charge current                                                                               |  |

| L1         | 23     | 0   | Switch output of step-down converter                                                                                                             |  |

| MODE       | 11     | I   | Pull HIGH to force the DCDC1 converter to PWM mode.                                                                                              |  |

| PB_IN      | 15     | I   | Push button input; Turns on DCDC1 and LDO1 if pulled to GND.                                                                                     |  |

| PGND       | 24     | _   | Power ground                                                                                                                                     |  |

| RESET      | 14     | 0   | Open-drain output of the reset generator; This output goes active LOW when the input voltage at pin THRESHOLD falls below the threshold voltage. |  |

| SCLK       | 8      | I   | Clock input for the I <sup>2</sup> C interface                                                                                                   |  |

| SDAT       | 12     | I/O | Data line for the I <sup>2</sup> C interface                                                                                                     |  |

| SYS        | 19, 20 | 0   | System voltage; output of the power path manager. Power input for step-down converter DCDC1                                                      |  |

| THRESHOLD  | 3      | I   | Input voltage to the reset comparator. When the input voltage falls below the threshold, the RESET output is actively pulled LOW.                |  |

| TS         | 27     | I   | Connect a thermistor from this pin to GND for battery temperature                                                                                |  |

| VINLDO1    | 30     | I   | Input voltage for LDO1                                                                                                                           |  |

| VLDO1      | 31     | 0   | Output voltage from LDO1                                                                                                                         |  |

| ThermalPad | _      | _   | Connect to GND                                                                                                                                   |  |

Copyright © 2009-2016, Texas Instruments Incorporated

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                      |                                                             | MIN   | MAX          | UNIT   |

|----------------------------------------------------------------------|-------------------------------------------------------------|-------|--------------|--------|

|                                                                      | All pins except A/PGND, AC, GPIOx pins with respect to AGND | -0.3  | 7            | V      |

| Input voltage                                                        | GPIOx pins with respect to AGND                             | -0.3  | VSYS         | V      |

|                                                                      | AC pin with respect to AGND                                 | -0.3  | 28           | V      |

| Voltage range on pin VLDO1, FB_LDO1, TS_OUT, TS with respect to AGND |                                                             |       | 3.6          | V      |

|                                                                      | AC, BAT, SYS, L1, VLDO1, VINLDO1, PGND                      |       | 600          | mA     |

| Current                                                              | GPIOx, AGND                                                 |       | 20           | mA     |

|                                                                      | All other pins                                              |       | 3            | mA     |

| Continuous total power dissipation                                   |                                                             | See D | issipation R | atings |

| Operating free-air temperature, T <sub>A</sub>                       |                                                             | -40   | 85           | °C     |

| Maximum junction temperature, T <sub>J</sub>                         |                                                             |       | 125          | °C     |

| Storage temperature, T <sub>stg</sub>                                |                                                             | -65   | 150          | °C     |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                    |                         |                                                                                        | VALUE | UNIT |

|--------------------|-------------------------|----------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (1)                       | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins $^{\rm (2)}$ | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

|                       |                                                                                                                       | MIN  | NOM | MAX      | UNIT |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------|------|-----|----------|------|

| V <sub>AC</sub>       | Input voltage at AC pin                                                                                               | 4.35 |     | 28       | V    |

| V <sub>SYS</sub>      | Voltage at SYS pin                                                                                                    | 2.2  |     | 5.6      | V    |

| I <sub>INUSB</sub>    | Input current at AC                                                                                                   |      |     | 500      | mA   |

| I <sub>OUTSYS</sub>   | Output current at SYS                                                                                                 |      |     | 400      | mA   |

| I <sub>BAT</sub>      | Average current into and out of BAT pin                                                                               |      |     | 300      | mA   |

| VINDCDC1              | Input voltage for step-down converter DCDC1                                                                           | 2.3  |     | 5.6      | V    |

| V <sub>DCDC1</sub>    | Output voltage for DCDC1 step-down converter; externally adjustable                                                   | 0.6  |     | VINDCDC1 | V    |

| IOUTDCDC1             | Output current at L                                                                                                   |      |     | 400      | mA   |

| L                     | Inductor at L <sup>(1)</sup>                                                                                          | 2.2  | 3.3 | 4.7      | μH   |

| V <sub>INLDO1</sub>   | Input voltage for LDO1                                                                                                | 1.8  |     | VSYS     | V    |

| V <sub>LDO1</sub>     | Output voltage for LDO1                                                                                               | 0.8  |     | 3.3      | V    |

| I <sub>LDO1</sub>     | Output current at LDO1                                                                                                |      |     | 200      | mA   |

| CINAC                 | Input capacitor at AC <sup>(1)</sup>                                                                                  | 0.1  |     | 1        | μF   |

| C <sub>BAT</sub>      | Capacitor at BAT <sup>(1)</sup>                                                                                       | 0.1  |     | 4.7      | μF   |

| C <sub>SYS</sub>      | Capacitor at SYS <sup>(1)</sup>                                                                                       | 4.7  |     | 10       | μF   |

| C <sub>INDCDC1</sub>  | Input capacitor at $V_{INDCDC1}^{(1)}$ ; if connected to SYS, only one 4.7-µF capacitor required for SYS and CINDCDC1 | 4.7  |     |          | μF   |

| C <sub>OUTDCDC1</sub> | Output capacitor at V <sub>DCDC1</sub> <sup>(1)</sup>                                                                 | 4.7  | 10  | 22       | μF   |

| C <sub>INLDO1</sub>   | Input capacitor at VINLDO1 <sup>(1)</sup>                                                                             | 2.2  |     |          | μF   |

| C <sub>OUTLDO1</sub>  | Output capacitor at LDO1 <sup>(1)</sup>                                                                               | 2.2  |     |          | μF   |

(1) See Application and Implementation for more details.

Copyright © 2009–2016, Texas Instruments Incorporated

#### TEXAS INSTRUMENTS

#### TPS65720, TPS657201, TPS657202, TPS65721

SLVS979B-OCTOBER 2009-REVISED OCTOBER 2016

www.ti.com

## **Recommended Operating Conditions (continued)**

|                   |                                                                                                                     | MIN | NOM MAX | UNIT |

|-------------------|---------------------------------------------------------------------------------------------------------------------|-----|---------|------|

| R <sub>ISET</sub> | Minimum R <sub>ISET</sub> value for proper operation; lower values may trigger the short circuit protection on ISET | 700 |         | Ω    |

| T <sub>A</sub>    | Operating ambient temperature                                                                                       | -40 | 85      | °C   |

| TJ                | Operating junction temperature                                                                                      | -40 | 125     | °C   |

# 7.4 Thermal Information

|                       |                                              | TPS65720    | TPS65721   |      |

|-----------------------|----------------------------------------------|-------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | YFF (DSBGA) | RSN (WQFN) | UNIT |

|                       |                                              | 25 PINS     | 32 PINS    |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 60.9        | 37.8       | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 0.4         | 28.2       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 11.3        | 8.6        | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 1.4         | 0.3        | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 11.3        | 8.5        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | n/a         | 2.6        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 7.5 Electrical Characteristics

$V_{SYS} = 3.6 \text{ V}, V_{DCDC1} = 2.05 \text{ V}, PFM \text{ mode}, L = 3.3 \mu\text{H}, C_{OUTDCDC1} = 4.7 \mu\text{F}, V_{INLDO1} = 2.05 \text{ V}, V_{LDO1} = 1.85 \text{ V}, T_A = -40^{\circ}\text{C}$  to 85°C typical values apply in a temperature range of 10°C to 35°C (unless otherwise noted)

|                                      | PARAMETER                                                                                                         | TEST CONDITIONS                                                                                                     | MIN                | TYP              | MAX              | UNIT |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------|------------------|------------------|------|

| SUPPLY CURREN                        | NT                                                                                                                | •                                                                                                                   |                    |                  |                  |      |

| lo                                   | Operating quiescent current when<br>only DCDC1 converter is enabled                                               | DCDC1 enabled, IOUT = 0 mA. PFM mode enabled; device not switching                                                  |                    | 36               | 45               | μA   |

|                                      | only Deber converter is enabled                                                                                   | DCDC1 enabled, IOUT = 0 mA. PWM mode                                                                                |                    | 2.8              |                  | mA   |

|                                      | Operating quiescent current when                                                                                  | Current into BAT pin (PFM mode)                                                                                     |                    | 33               | 50               | μA   |

| l <sub>Q</sub>                       | LDO1 and DCDC1 are enabled                                                                                        | Current into VINLDO1                                                                                                |                    | 13               | 18               | μA   |

|                                      | Shutdown current after voltage was<br>applied to BAT but device never<br>enabled before (shipping mode)           | For VINLDO1 = 0 V (LDO1 supplied by DCDC1); powered by VBAT = 3.6 V                                                 |                    | 4                | 13               | μΑ   |

| I <sub>SD</sub>                      | Shutdown current after first power-<br>up                                                                         | For VINLDO1 = 0 V (LDO1 supplied by DCDC1); powered by VBAT = 3.6 V                                                 |                    | 12               | 17               | μΑ   |

|                                      | Shutdown current after first power-<br>up                                                                         | For VINLDO1 $\neq$ 0 V (LDO1 supplied by SYS); powered by VBAT = 3.6 V                                              |                    | 12               | 18               | μΑ   |

| SDAT, SCLK, PB                       | IN, HOLD, GPIO0 TO GPIO3, INT, RE                                                                                 | SET, THRESHOLD                                                                                                      |                    |                  |                  |      |

| V <sub>IH</sub>                      | High-level input voltage for SCLK,<br>SDAT, GPIOx, HOLD_DCDC1,<br>HOLD_LDO1, PB_IN                                | GPIOs configured as input                                                                                           | 1.2                |                  | VSYS             | V    |

| V <sub>IL</sub>                      | Low-level input voltage for SCLK,<br>SDAT, GPIOx, <u>HOLD_DCDC1,</u><br>HOLD_LDO1, PB_IN                          | GPIOs configured as input                                                                                           | 0                  |                  | 0.4              | V    |

| V <sub>OL</sub>                      | Low-level output voltage for SDAT, GPIOx, INT, RESET                                                              | GPIOs configured as output; $I_{\rm o}$ = 1 mA; no internal pull-up                                                 | 0                  |                  | 0.4              | V    |

| I <sub>OL</sub>                      | Sink current for GPIO2, GPIO3                                                                                     | GPIO2, GPIO3 configured as current sink; $V_{OL}$ = 0.4 V ; for $T_{J}$ = 0°C to 85°C                               | -20%               | 5                | 20%              | mA   |

|                                      | Sink current for GPIOx                                                                                            | GPIOx configured as open-drain output ; output = LOW                                                                |                    |                  | 3                | mA   |

| V <sub>OL</sub>                      | Minimum voltage for proper current<br>regulation from GPIO2 or GPIO3 to<br>GND if programmed as a current<br>sink | I <sub>o</sub> = 5 mA; current sink turned on                                                                       | 0.4                |                  |                  | V    |

| V <sub>RESET-falling</sub>           | LDO1 out of regulation reset                                                                                      | Falling edge; RESET is asserted LOW for TPS65720, TPS657201, TPS657202                                              | VLDO1, nom-<br>13% |                  | VLDO1,<br>nom-7% | V    |

| $V_{RESET-rising}$                   | voltage                                                                                                           | Rising edge; $\overline{\text{RESET}}$ is released HIGH for TPS65720, TPS657201, TPS657202 after $T_{\text{RESET}}$ |                    | VLDO1,<br>nom-4% |                  | V    |

| $V_{\text{THRESHOLD}_{\text{down}}}$ | Threshold voltage for reset input                                                                                 | Falling voltage; WQFN package only                                                                                  | -3%                | 570              | 3%               | mV   |

| $V_{\text{THRESHOLD_hys}}$           | Hysteresis on THRESHOLD                                                                                           | Rising voltage; WQFN package only                                                                                   |                    | 30               |                  | mV   |

| I <sub>LKG</sub>                     | Input leakage current                                                                                             | PB_IN, SDAT, SCLK, GPIOx configured as output, INT, RESET, output high impedance                                    |                    |                  | 0.2              | μΑ   |

## **Electrical Characteristics (continued)**

$V_{SYS} = 3.6 \text{ V}, V_{DCDC1} = 2.05 \text{ V}, \text{ PFM mode, } L = 3.3 \text{ }\mu\text{H}, \text{ }C_{OUTDCDC1} = 4.7 \text{ }\mu\text{F}, \text{ }V_{\text{INLDO1}} = 2.05 \text{ }V, \text{ }V_{\text{LDO1}} = 1.85 \text{ }V, \text{ }T_{\text{A}} = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C} \text{ typical values apply in a temperature range of } 10^{\circ}\text{C to } 35^{\circ}\text{C} \text{ (unless otherwise noted)}$

|                             | PARAMETER                                                 | TEST CONDITIONS                                                                                                    | MIN                | TYP               | MAX               | UNIT  |

|-----------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------|-------------------|-------------------|-------|

| STEP-DOWN C                 | ONVERTER                                                  |                                                                                                                    |                    |                   |                   |       |

| V <sub>SYS</sub>            | Input voltage for DCDC1                                   |                                                                                                                    | 2.3                |                   | 5.6               | V     |

| UVLO                        | Internal undervoltage lockout                             | V <sub>SYS</sub> falling                                                                                           | 2.15               | 2.2               | 2.25              | V     |

| UVLO                        | threshold hysteresis                                      | V <sub>SYS</sub> rising                                                                                            |                    | 120               |                   | mV    |

| POWER SWITC                 | н                                                         |                                                                                                                    |                    |                   |                   |       |

| P                           |                                                           | V <sub>SYS</sub> = V <sub>INDCDC1</sub> = 3.6 V, YFF package                                                       |                    | 350               | 600               | mΩ    |

| R <sub>DS(ON)</sub>         | High-side MOSFET ON-resistance                            | V <sub>SYS</sub> = V <sub>INDCDC1</sub> = 3.6 V, RSN package                                                       |                    | 400               | 650               | 11175 |

| I <sub>LK_HS</sub>          | High-side MOSFET leakage current                          | V <sub>DS</sub> = 5.6 V                                                                                            |                    |                   | 1                 | μA    |

| P                           | Low-side MOSFET ON-resistance                             | V <sub>INDCDC1/2</sub> = 3.6 V, YFF package                                                                        |                    | 300               | 500               | mΩ    |

| R <sub>DS(ON)</sub>         | Low-side MOSFET ON-resistance                             | V <sub>INDCDC1/2</sub> = 3.6 V, RSN package                                                                        |                    | 350               | 550               | mΩ    |

| I <sub>LK_LS</sub>          | Low-side MOSFET leakage current                           | VDS = 5.6 V                                                                                                        |                    |                   | 1                 | μA    |

|                             | Forward current limit high-side and                       | $2.3 \text{ V} \le \text{V}_{\text{IN}} \le 5.6 \text{ V}, \text{TPS65720}$                                        | 425                | 600               | 775               | mA    |

| LIMF                        | low-side MOSFET                                           | $2.3 \text{ V} \le \text{V}_{\text{IN}} \le 5.6 \text{ V}, \text{ TPS65721}, \text{ TPS657201}, \text{ TPS657202}$ | 625                | 850               | 1150              | mA    |

|                             | DC sutsut surrent                                         | V <sub>SYS</sub> > 2.7 V; TPS65720                                                                                 |                    |                   | 200               | mA    |

| lo                          | DC output current                                         | V <sub>SYS</sub> > 2.7 V; TPS65721, TPS657201, TPS657202                                                           |                    |                   | 400               | mA    |

| OUTPUT                      |                                                           |                                                                                                                    |                    |                   |                   |       |

| V <sub>OUT</sub>            | Output voltage range                                      |                                                                                                                    | 0.6                |                   | Vin               | V     |

| V <sub>FB</sub>             | Feedback voltage                                          | for TPS65720, TPS65721                                                                                             |                    | 0.6               |                   | V     |

| V <sub>OUT</sub>            | Default output voltage for<br>TPS657201                   |                                                                                                                    |                    | 1.85              |                   | V     |

| V <sub>OUT</sub>            | Default output voltage for<br>TPS657202                   |                                                                                                                    |                    | 1.90              |                   | V     |

| I <sub>FB</sub>             | FB pin input current for externally<br>adjustable version | External resistor-divider                                                                                          |                    |                   | 0.1               | μΑ    |

| I <sub>FB</sub>             | FB pin input current for TPS657201, TPS657202             | Internal resistor-divider                                                                                          |                    |                   | 5                 | μΑ    |

|                             |                                                           | $V_{\text{IN}}$ = 2.3 V to 5.6 V; PFM operation, 0 mA < I_{\text{OUT}} < I_{\text{OUTMAX}}                         |                    | 1%                | 3%                |       |

| V <sub>OUT</sub>            | DC output voltage accuracy <sup>(1)</sup>                 | $V_{\text{IN}}$ = 2.3 V to 5.6 V, PWM operation, 0 mA < I_{\text{OUT}} < I_{\text{OUTMAX}}                         | -2%                |                   | 2%                |       |

|                             | DC output voltage load regulation                         | PWM operation                                                                                                      |                    | 0.5               |                   | %/A   |

| V <sub>PGOOD</sub> -falling | PGOOD threshold at falling output voltage                 | <pgoodz_dcdc1> is set to 1</pgoodz_dcdc1>                                                                          | VDCDC1,<br>nom-14% |                   | VDCDC1,<br>nom-7% | V     |

| V <sub>PGOOD</sub> -rising  | PGOOD threshold at rising output voltage                  | <pgoodz_dcdc1> is set to 0</pgoodz_dcdc1>                                                                          |                    | VDCDC1,<br>nom-5% |                   | V     |

| R <sub>DIS</sub>            | Internal discharge resistor at L                          | DCDC1 disabled; the discharge function can be disabled as an<br>EEPROM option                                      | 300                | 400               |                   | Ω     |

| THERMAL PRO                 | TECTION FOR DCDC1 AND LDO1                                | ·                                                                                                                  |                    |                   |                   |       |

| T <sub>SD</sub>             | Thermal shutdown                                          | Increasing junction temperature                                                                                    |                    | 150               |                   | °C    |

|                             | Thermal shutdown hysteresis                               | Decreasing junction temperature                                                                                    |                    | 30                |                   | °C    |

(1) Output voltage specification does not include tolerance of external voltage programming resistors.

SLVS979B-OCTOBER 2009-REVISED OCTOBER 2016

www.ti.com

# **Electrical Characteristics (continued)**

$V_{SYS}$  = 3.6 V,  $V_{DCDC1}$  = 2.05 V, PFM mode, L = 3.3  $\mu$ H,  $C_{OUTDCDC1}$  = 4.7  $\mu$ F,  $V_{INLDO1}$  = 2.05 V,  $V_{LDO1}$  = 1.85 V,  $T_A$  = -40°C to 85°C typical values apply in a temperature range of 10°C to 35°C (unless otherwise noted)

|                        | PARAMETER                                                                               | TEST CONDITIONS                                                                             | MIN        | TYP   | MAX  | UNIT |

|------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------|-------|------|------|

| VLDO1 LOW D            | ROPOUT REGULATOR                                                                        |                                                                                             |            |       |      |      |

| V <sub>INLDO</sub>     | Input voltage range for LDO1                                                            |                                                                                             | 1.8        |       | 5.6  | V    |

| V <sub>LDO1</sub>      | LDO1 output voltage range                                                               |                                                                                             | 0.8        |       | 3.3  | V    |

| V <sub>LDO1</sub>      | LDO1 output voltage                                                                     | Default output voltage for TPS65720, TPS657201                                              |            | 1.85  |      | V    |

| V <sub>LDO1</sub>      | LDO1 output voltage                                                                     | Default output voltage for TPS657202                                                        |            | 2.85  |      | V    |

| V <sub>FB_LDO1</sub>   | Feedback voltage                                                                        | Externally adjustable version only: TPS65721                                                |            | 0.8   |      | V    |

| I <sub>FB_LDO1</sub>   | FB pin input current                                                                    |                                                                                             |            |       | 0.1  | μA   |

| I <sub>0</sub>         | Output current for LDO1                                                                 |                                                                                             |            |       | 200  | mA   |

| I <sub>sc</sub>        | LDO1 short circuit current limit                                                        | VLDO1 = GND; V <sub>INLDO1</sub> = 2.05 V                                                   |            | 350   | 500  | mA   |

|                        | Dropout voltage at LDO1, YFF package                                                    | I <sub>O</sub> = 200 mA, V <sub>INLDO</sub> = 2.05 V                                        |            |       | 180  | mV   |

|                        | Dropout voltage at LDO1, RSN package                                                    | I <sub>O</sub> = 200 mA, V <sub>INLDO</sub> = 2.05 V                                        |            | 120   |      | mV   |

|                        | Output voltage accuracy for LDO1                                                        | I <sub>O</sub> = 200 mA                                                                     | -1.5%      |       | 2.5% |      |

|                        | Line regulation for LDO1                                                                | $V_{\rm INLDO1}$ = $V_{\rm LDO1}$ + 0.5 V (min. 1.8 V) to 5.6 V (VSYS), $I_{\rm O}$ = 50 mA | -1%        |       | 1%   |      |

|                        | Load regulation for LDO1                                                                | I <sub>O</sub> = 0 mA to 200 mA for LDO1                                                    | -1%        |       | 2%   |      |

| R <sub>DIS</sub>       | Internal discharge resistor at VLDO1                                                    | LDO disabled, discharge function per default disabled in register                           | 250        | 400   |      | Ω    |

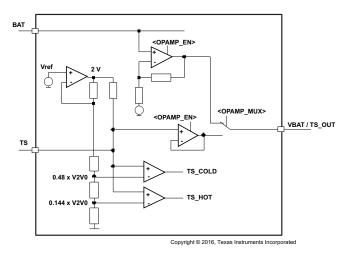

| BATTERY VOL            | TAGE AND BATTERY TEMPERATURE                                                            | MONITOR WITH MULTIPLEXER; INTERNAL BATTERY VOLTAGE                                          | COMPARATOR |       |      |      |

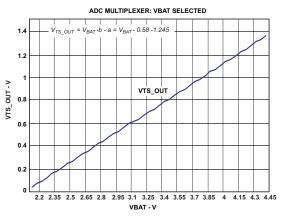

| V <sub>TS</sub>        | Input voltage range on TS pin for<br>full scale output on pin TS_OUT<br>(0 V to 1.4 V)  | Equals –20°C to 60°C on a 10k NTC                                                           | 0          |       | 1.4  | V    |

| V <sub>BAT</sub>       | Input voltage range on BAT pin for<br>full scale output on pin TS_OUT<br>(0 V to 1.4 V) |                                                                                             | 2.2        |       | 4.5  | V    |

|                        | Output voltage range on pin                                                             | I <sub>TS_OUT</sub> = 0 mA                                                                  | 0          |       | 1.4  |      |

| V <sub>TS_OUT</sub>    | TS_OUT                                                                                  | 0 < I <sub>TS_OUT</sub> < 0.05 mA                                                           | 0.06       |       | 1.4  | V    |

|                        | Offset error on pin TS_OUT                                                              | In temperature-sense mode; $V_0$ with $V_{bat} = 2.2$ V                                     |            |       | ±7.5 | mV   |

| SR                     | Slew rate                                                                               | V <sub>TS OUT</sub> ; 0 V to 1.4 V                                                          |            | 1     |      | V/ms |

| I <sub>TS_OUT_SC</sub> | Short circuit current                                                                   | .13_0019 4 1 6                                                                              | 0.1        |       |      | mA   |

| 13_001_30              | Load capacitance                                                                        | Maximum capacitance at TS_OUT                                                               | -          |       | 100  | pF   |

|                        | Battery voltage comparator<br>threshold voltage                                         | Depending on Bits <vbat0>, <vbat1>; falling voltage</vbat1></vbat0>                         | -3%        |       | 3%   | V    |

|                        | Battery voltage comparator threshold voltage hysteresis                                 | Rising voltage                                                                              |            | 200   |      | mV   |

| ACCURACY               |                                                                                         | · · · ·                                                                                     |            |       |      |      |

| VBAT MODE              |                                                                                         |                                                                                             |            |       |      |      |

|                        | Offset                                                                                  | $T_J = 10^{\circ}C \text{ to } 35^{\circ}; \text{ for V(TS)} \ge 0.2 \text{ V}$             | -22        |       | 22   | mV   |

|                        | Gain error                                                                              | $T_J = 10^{\circ}C \text{ to } 35^{\circ}; \text{ for V(TS)} \ge 0.2 \text{ V}$             | -11        |       | 11   | mV   |

|                        | Offset                                                                                  | $T_J = -40^{\circ}C$ to 85°C; for V(TS) $\ge 0.2$ V                                         | -30        |       | 30   | mV   |

|                        | Gain error                                                                              | $T_J = -40^{\circ}C$ to 85°C; for V(TS) $\ge 0.2$ V                                         | -14        |       | 14   | mV   |

| TS MODE                |                                                                                         | · · ·                                                                                       |            |       |      |      |

|                        | Internal TS resistor (for 10k NTC,<br>B=3380)                                           | $T_J = 25^{\circ}C$                                                                         | -1.5%      | 29.23 | 1.5% | kΩ   |

|                        | Internal TS resistor (for 100k NTC)                                                     | $T_J = 25^{\circ}C$                                                                         | -1.5%      | 292.3 | 1.5% | kΩ   |

|                        | Internal TS resistor temperature drift                                                  | $T_{\rm J} = -40^{\circ}$ C to 85°C                                                         |            | -4.5% |      |      |

|                        | Internal V2V0 reference voltage                                                         | $T_{\rm J} = -40^{\circ}$ C to 85°C                                                         | -1.2%      | 2     | 1.2% | V    |

# **Electrical Characteristics (continued)**

$V_{SYS}$  = 3.6 V,  $V_{DCDC1}$  = 2.05 V, PFM mode, L = 3.3  $\mu$ H,  $C_{OUTDCDC1}$  = 4.7  $\mu$ F,  $V_{INLDO1}$  = 2.05 V,  $V_{LDO1}$  = 1.85 V,  $T_A$  = -40°C to 85°C typical values apply in a temperature range of 10°C to 35°C (unless otherwise noted)

|                          | PARAMETER                                                                                                      | TEST CONDITIONS                                                                                                                                                                                                        | MIN    | TYP                                               | MAX  | UNIT |

|--------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------------------|------|------|

| POWER PATH               | FANAMETER                                                                                                      | TEST CONDITIONS                                                                                                                                                                                                        | IVIIIN | IIF                                               | WIAA | UNIT |

| V <sub>UVLO</sub>        | Undervoltage lockout                                                                                           | $V_{AC}$ : 0 V $\rightarrow$ 4 V                                                                                                                                                                                       | 3.2    | 3.3                                               | 3.45 | V    |

| V <sub>UVLO</sub>        | Hysteresis on UVLO                                                                                             | $V_{AC}: 0 \lor \rightarrow 4 \lor 0$ $V_{AC}: 4 \lor \rightarrow 0 \lor 0$                                                                                                                                            | 200    | 5.5                                               | 3.43 | mV   |

| V <sub>IN-DT</sub>       | Input power detection threshold                                                                                | $ \begin{array}{l} (\text{Input power detected if } V_{\text{IN}} > V_{\text{BAT}} + V_{\text{IN-DT}}) \ V_{\text{BAT}} = 3.6 \ \text{V}, \\ V_{\text{IN}} \cdot 3.5 \ \text{V} \rightarrow 4 \ \text{V} \end{array} $ | 40     | 80                                                | 140  | mV   |

| V <sub>HYS-INDT</sub>    | Hysteresis on VIN-DT                                                                                           | $V_{\text{IN}}$ . 3.5 V $\rightarrow$ 4 V<br>V <sub>BAT</sub> = 3.6 V, V <sub>IN</sub> : 4 V $\rightarrow$ 3.5 V                                                                                                       | 20     |                                                   |      | mV   |

| V <sub>OVP</sub>         | Input overvoltage protection                                                                                   | $V_{AC}: 5 \vee \rightarrow 7 \vee$                                                                                                                                                                                    | 6.4    | 6.6                                               | 6.8  | V    |

|                          | threshold                                                                                                      |                                                                                                                                                                                                                        |        |                                                   |      |      |

| V <sub>HYS-OVP</sub>     | Hysteresis on OVP                                                                                              | $V_{AC}$ : 11 V $\rightarrow$ 5 V                                                                                                                                                                                      |        | 105                                               | 005  | mV   |

| V <sub>DO(AC-SYS)</sub>  | AC pin to SYS pin dropout voltage $V_{AC} - V_{SYS}$                                                           | $I_{SYS} = 0.3 \text{ A}, V_{AC} = 4.35 \text{ V}, V_{BAT} = 4.2 \text{ V}; \text{ YFF package}$                                                                                                                       |        | 170                                               | 285  | mV   |

|                          |                                                                                                                | $I_{SYS} = 0.3 \text{ A}, V_{AC} = 4.35 \text{ V}, V_{BAT} = 4.2 \text{ V}; \text{ RSN package}$                                                                                                                       |        | 210                                               | 325  | mV   |

| V <sub>DO(BAT-SYS)</sub> | Battery to SYS pin dropout voltage<br>V <sub>BAT</sub> – V <sub>SYS</sub>                                      | $I_{SYS} = 0.2 \text{ A}, V_{AC} = 0 \text{ V}, V_{BAT} > 3 \text{ V}; \text{ YFF package}$                                                                                                                            |        |                                                   | 80   | mV   |

|                          | BAT SYS                                                                                                        | $I_{SYS} = 0.2 \text{ A}, V_{AC} = 0 \text{ V}, V_{BAT} > 3 \text{ V}; \text{ RSN package}$                                                                                                                            | 50/    |                                                   | 120  | mV   |

|                          |                                                                                                                | $00: V_{AC} > V_{SYS} + V_{DO(AC-SYS)}, V_{BAT} < 3.3V$                                                                                                                                                                | -5%    | 3.4                                               | 5%   |      |

|                          | SYS pin voltage regulation<br>selectable register                                                              | 00: $V_{AC} > V_{SYS} + V_{DO(AC-SYS)}$ , $V_{BAT} \ge 3.3 \text{ V}$                                                                                                                                                  | -5%    | V <sub>BAT</sub> +<br>200 mV                      | 5%   | .,   |

| V <sub>SYS(REG)</sub>    | <chgconfig0> Bits <vsys1>;</vsys1></chgconfig0>                                                                | 01: $V_{AC} > V_{SYS} + V_{DO(AC-SYS)}$                                                                                                                                                                                | -5%    | 4.4                                               | 5%   | V    |

|                          | <vsys0></vsys0>                                                                                                | 10: $V_{AC} > V_{SYS} + V_{DO(AC-SYS)}$                                                                                                                                                                                | -5%    | 5.0                                               | 5%   |      |

|                          |                                                                                                                | 11: $V_{AC} > V_{SYS} + V_{DO(AC-SYS)}$                                                                                                                                                                                | -5%    | 5.5                                               | 5%   |      |

|                          | Maximum Input Current Register                                                                                 | Bit <ac ac="" current0="" current1,="" input=""> = 00</ac>                                                                                                                                                             | 90     | 95                                                | 100  |      |

| I <sub>AC-MAX</sub>      | <chconfig0></chconfig0>                                                                                        | Bit < AC input current1, AC input current0> = 01 or 10                                                                                                                                                                 | 450    | 475                                               | 500  | mA   |

| V <sub>AC-LOW</sub>      | Input voltage threshold when input<br>current is reduced                                                       | Input current is reduced if voltage at AC falls below VAC-LOW to keep the AC voltage above 4.5 V $$                                                                                                                    | 4.35   | 4.5                                               | 4.65 | V    |

| V <sub>DPM</sub>         | Output voltage threshold when<br>charging current is reduced                                                   | Bit <v_dppm> = 1</v_dppm>                                                                                                                                                                                              |        | V <sub>O(REG)</sub> –<br>100 mV                   |      | V    |

| • DPM                    | Register <chconfig2></chconfig2>                                                                               | Bit <v_dppm> = 0</v_dppm>                                                                                                                                                                                              |        | 4.3                                               |      | •    |

|                          |                                                                                                                |                                                                                                                                                                                                                        |        | V <sub>OUT</sub> ≤                                |      |      |

| V <sub>BSUP1</sub>       | Enter battery supplement mode                                                                                  |                                                                                                                                                                                                                        |        | V <sub>BAT</sub> –<br>40 mV                       |      | V    |

| V <sub>BSUP2</sub>       | Exit battery supplement mode                                                                                   |                                                                                                                                                                                                                        |        | V <sub>OUT</sub> ≥<br>V <sub>BAT</sub> –<br>20 mV |      | V    |

| V <sub>O(SC1)</sub>      | Output short-circuit detection threshold, power-on                                                             |                                                                                                                                                                                                                        | 0.8    | 0.9                                               | 1    | V    |

| V <sub>O(SC2)</sub>      | Output short-circuit detection threshold, supplement mode $V_{BAT}-V_{OUT}>V_{O(SC2)}$ indicates short-circuit |                                                                                                                                                                                                                        | 200    | 250                                               | 300  | mV   |

| BATTERY CHAR             | RGER                                                                                                           |                                                                                                                                                                                                                        |        |                                                   |      |      |

| QUIESCENT CU             | RRENT                                                                                                          |                                                                                                                                                                                                                        |        |                                                   |      |      |

|                          | Standby current into AC pin                                                                                    | V <sub>IN</sub> = 5 V; ACinputcurrent[1,0] = 11                                                                                                                                                                        |        | 60                                                | 80   | μA   |

| IACSTDBY)                | Standby current into AC pin                                                                                    | V <sub>IN</sub> = 28 V; ACinputcurrent[1,0] = 11                                                                                                                                                                       |        |                                                   | 530  | μA   |

| I <sub>cc</sub>          | Active supply current, AC pin                                                                                  | $V_{IN} = 5 V$ , no load on DCDC1, LDO1, SYS pin, VSYS[1,0] = 11;<br>ACinputcurrent[1,0] = 10; CH_EN = 0                                                                                                               |        |                                                   | 2    | mA   |

| IBAT(SC)                 | Source current for BAT pin short-<br>circuit detection                                                         |                                                                                                                                                                                                                        | 4      | 7.5                                               | 11   | mA   |

| VBAT(SC)                 | BAT pin short-circuit detection threshold                                                                      |                                                                                                                                                                                                                        | 1.6    | 1.8                                               | 2.0  | V    |

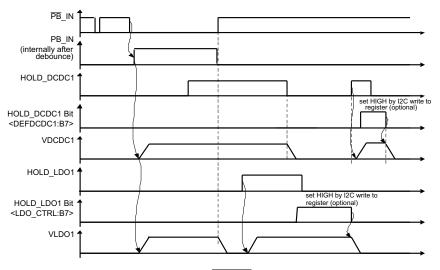

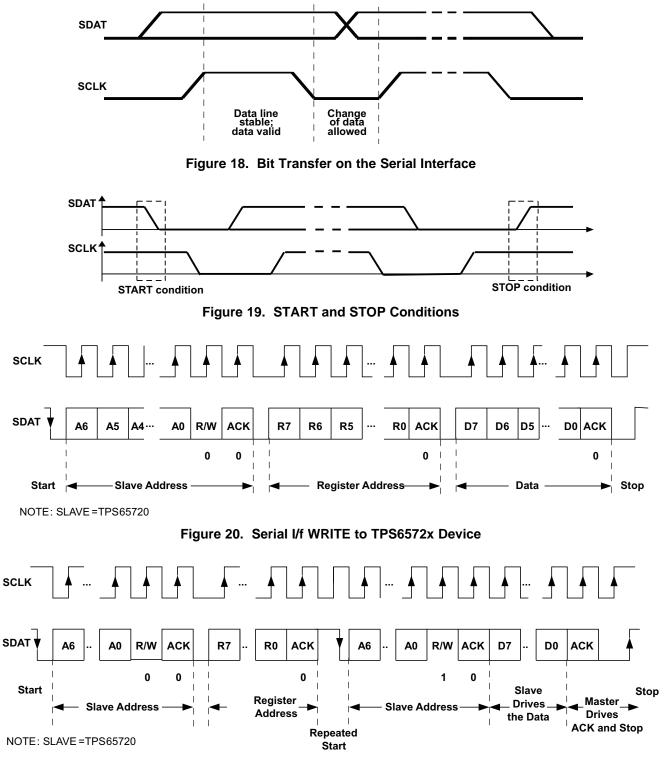

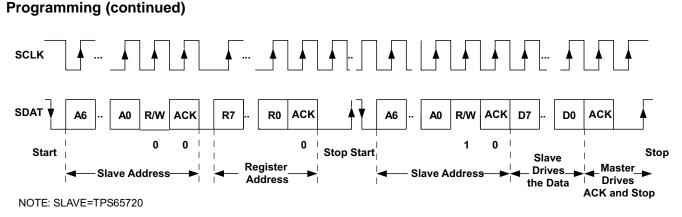

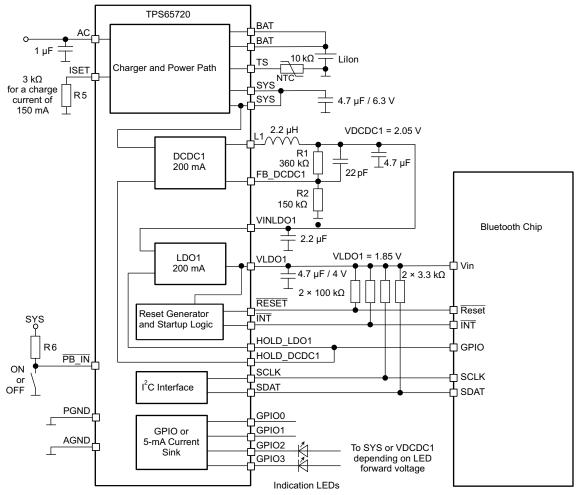

|                          |                                                                                                                |                                                                                                                                                                                                                        | -1%    | 4.15                                              | 1%   |      |