# AK8970N

# **Electronic Compass**

|                                                                           | Features                                                                                 |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Terrestrial magnetism detection type electronic compass module            |                                                                                          |  |  |  |  |  |  |  |

| ☐ Built-in 3 high sensitiv                                                | ity Hall devices                                                                         |  |  |  |  |  |  |  |

| ☐ Functions                                                               |                                                                                          |  |  |  |  |  |  |  |

| <ul> <li>Built-in</li> </ul>                                              | a magnetic sensors for detecting the terrestrial magnetism in the X, Y, and Z directions |  |  |  |  |  |  |  |

| <ul><li>Built-in</li></ul>                                                | a 8-bit A/D converter for digital outputs                                                |  |  |  |  |  |  |  |

| • Built-in                                                                | 8-bit D/A converter for offset magnetic field correction                                 |  |  |  |  |  |  |  |

| Built-in                                                                  | EEPROM for Hall device sensitivity calibration                                           |  |  |  |  |  |  |  |

| <ul> <li>Serial in</li> </ul>                                             | nterface (the low-voltage specification also applicable)                                 |  |  |  |  |  |  |  |

| <ul> <li>Auto po</li> </ul>                                               | ower-down and Interrupt output function                                                  |  |  |  |  |  |  |  |

| <ul> <li>Operab</li> </ul>                                                | le with a 11MHz to 26MHz of master clock                                                 |  |  |  |  |  |  |  |

| Selecta                                                                   | ble between clipped sine wave and CMOS level rectangular wave input                      |  |  |  |  |  |  |  |

| ☐ Operating temperature                                                   | : -30°C to +85°C                                                                         |  |  |  |  |  |  |  |

| ☐ Operating supply volta                                                  | ge: +2.5V to +3.6V                                                                       |  |  |  |  |  |  |  |

| ☐ Low power consumption                                                   | on: 8.5mA typ. @measurement                                                              |  |  |  |  |  |  |  |

| 0.1 μ A typ. @power down  ☐ Measurement time : 38.1msec. @MCLK=11.2896MHz |                                                                                          |  |  |  |  |  |  |  |

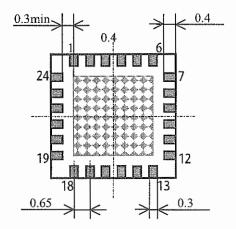

| □ Package                                                                 | : 24-pin QFN (multi-chip module) 5.0mm × 5.0mm × 1.0mm [AK8970N]                         |  |  |  |  |  |  |  |

|                                                                           |                                                                                          |  |  |  |  |  |  |  |

# **General Description**

The AK8970N is a terrestrial magnetism detection type electronic compass module and is designed to provide azimuth information for cell phones and PDAs having GPS functions by incorporating the correction & calculation software supplied by AKM in the system. This module includes three Hall devices with orthogonal orientation for detecting the terrestrial magnetism in the X, Y, and Z directions, therefore allowing compact products to be realized.

The AK8970N has the following features:

- (1) By using high sensitivity Hall devices, advanced mixed signal processing technology and proprietary digital correction technology, terrestrial magnetism signal detection by Hall devices is made possible.

- (2) With the built-in 8-bit A/D converter and serial interface, the X-, Y-, and Z-direction component signals of the terrestrial magnetism are output in a digital form.

MS-0370-E-00 - 1 - 12/2004

- (3) A separate power supply is used for the serial interface, so the low-voltage specification can also be supported by applying 1.85V.

- (4) The built-in D/A converter can be used to compensate the offset magnetic field.

- (5) The built-in EEPROM is used to store Hall devices sensitivity. The calibration values for the Hall device sensitivity are factory-set in the EEPROM.

- (6) The value of the built-in temperature sensor is output in a digital form through the ADC.

- (7) Main circuit blocks of the IC are started by measurement request commands from the controller, and power-down mode is entered automatically after the measurement finished.

- (8) An interrupt function to notify the external controller of the end of measurement is included.

- (9) Master clock frequencies ranging from 11MHz to 26MHz can be used.

- (10) AKM provides software (functions) for azimuth calculation and preceding correction processing, which are performed based on the values measured by the AK8970N.

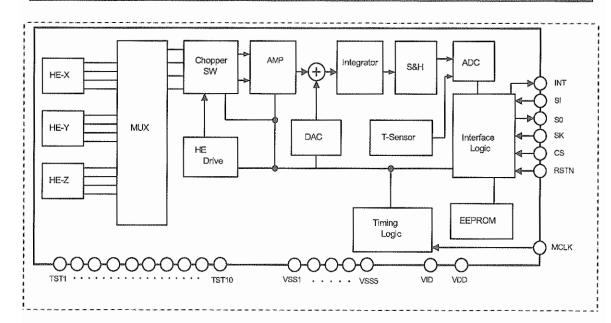

## Block Diagram

# Circuit Configuration

| Block            | Function                                                                                                                                                                                                                                                                           |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HE-X, HE-Y, HE-Z | High sensitivity Hall devices included in the package                                                                                                                                                                                                                              |

| MUX              | Matrix switch for selecting one of the three                                                                                                                                                                                                                                       |

| Chopper SW       | Performs chopping to reduce an offset of Hall device.                                                                                                                                                                                                                              |

| HE Drive         | Hall device drive circuit for 0.5V.                                                                                                                                                                                                                                                |

| AMP.             | Variable-gain differential amplifier to amplify the Hall device signal and adjust the sensitivity.                                                                                                                                                                                 |

|                  | Setting gain: 18.2dB min., increased in 0.3dB steps, 32 steps (5 bits)                                                                                                                                                                                                             |

| DAC              | D/A converter for offset magnetic field compensation Resolution: 8 bits, step width: 100μV, setting accuracy: 1/4LSB                                                                                                                                                               |

| Integrator       | Integrates the output signals from AMP., amplifies voltage, and reduces noise.                                                                                                                                                                                                     |

| S&H              | Sample & Hold circuit                                                                                                                                                                                                                                                              |

| ADC              | Performs analog-to-digital conversion for the Hall device and temperature sensor signals. Resolution: 8 bits                                                                                                                                                                       |

| T-Sensor         | Temperature sensor to convert temperature to voltage                                                                                                                                                                                                                               |

| Interface Logic  | Serial interface circuits for data transfer with an external controller through four pins SK, SI, SO, and CS. The external controller is notified of the end of measurement through the INT pin.  The low-voltage specification can be supported by applying 1.85V to the VID pin. |

| Timing Logic     | Based on the 11MHz to 26MHz master clock input from the MCLK pin, internal timing clock pulses are generated.                                                                                                                                                                      |

| EEPROM           | Nonvolatile memory. This memory is read from and written to through four pins SK, SI, SO, and CS.                                                                                                                                                                                  |

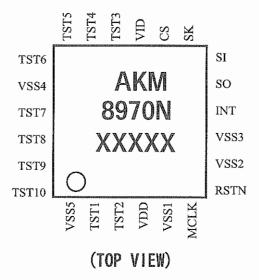

# Pin Functions

| No | Pin name | I/O | Туре   | Function                                                                                                                                                                                                                                                                                                                                     |  |  |

|----|----------|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1  | VSS5     | _   | Power  | Ground pin                                                                                                                                                                                                                                                                                                                                   |  |  |

| 2  | TST1     | I/O | Analog | Test pins used for factory testing.                                                                                                                                                                                                                                                                                                          |  |  |

| 3  | TST2     | 1/0 | Analog | Leave these pins open individually, without wiring.                                                                                                                                                                                                                                                                                          |  |  |

| 4  | VDD      | _   | Power  | Positive power supply pin                                                                                                                                                                                                                                                                                                                    |  |  |

| 5  | VSS1     | _   | Power  | Ground pin                                                                                                                                                                                                                                                                                                                                   |  |  |

| 6  | MCLK     | l   | CMOS   | Master clock input pin 11MHz to 26MHz clock is input.                                                                                                                                                                                                                                                                                        |  |  |

| 7  | RSTN     | l   | CMOS   | Reset input pin "L" causes a reset, and power-down mode is entered.                                                                                                                                                                                                                                                                          |  |  |

| 8  | VSS2     | _   | Power  | Ground pin                                                                                                                                                                                                                                                                                                                                   |  |  |

| 9  | VSS3     | _   | Power  | Ground pin                                                                                                                                                                                                                                                                                                                                   |  |  |

| 10 | INT      | 0   | CMOS   | Interrupt signal output pin Normally "L". When measurement finished, "H" is output.                                                                                                                                                                                                                                                          |  |  |

| 11 | SO       | 0   | CMOS   | Serial data and EEPROM data output pin                                                                                                                                                                                                                                                                                                       |  |  |

| 12 | SI       | ı   | CMOS   | Serial data and EEPROM data input pin                                                                                                                                                                                                                                                                                                        |  |  |

| 13 | SK       | 1   | CMOS   | Serial data and EEPROM data clock input pin                                                                                                                                                                                                                                                                                                  |  |  |

| 14 | cs       | 1   | CMOS   | Serial data and EEPROM data I/O chip select input pin Active high                                                                                                                                                                                                                                                                            |  |  |

| 15 | VID      | -   | Power  | Digital interface positive power supply pin This pin is a positive power supply pin for the digital interface block. By connecting this pin to a 1.85V power supply, the low-voltage specification digital interface can be connected. For use of the normal CMOS-level interface, connect this pin to the same power supply as that of VDD. |  |  |

| 16 | TST3     | I/O | Analog | Test pins used for factory testing.                                                                                                                                                                                                                                                                                                          |  |  |

| 17 | TST4     | I/O | Analog | Leave these pins open individually, without wiring.                                                                                                                                                                                                                                                                                          |  |  |

| 18 | TST5     | I/O | Analog |                                                                                                                                                                                                                                                                                                                                              |  |  |

| 19 | TST6     | 1/0 | Analog |                                                                                                                                                                                                                                                                                                                                              |  |  |

| 20 | VSS4     | _   | Power  | Ground pin                                                                                                                                                                                                                                                                                                                                   |  |  |

| 21 | TST7     | 1/0 | Analog | Test pins used for factory testing.                                                                                                                                                                                                                                                                                                          |  |  |

| 22 | TST8     | 1/0 | Analog | Leave these pins open individually, without wiring.                                                                                                                                                                                                                                                                                          |  |  |

| 23 | TST9     | I/O | Analog |                                                                                                                                                                                                                                                                                                                                              |  |  |

| 24 | TST10    | 1/0 | Analog |                                                                                                                                                                                                                                                                                                                                              |  |  |

<sup>\*</sup>VSS1~VSS5 are connected internally. It is not necessary to connect threes all 5 pins to Ground, but VSS1(pin#5) must be connected to Ground at least.

MS-0370-E-00 - 4 - 12/2004

# Absolute Maximum Ratings

VSS = 0V

| Parameter                       | Symbol | Min. | Max.       | Unit |

|---------------------------------|--------|------|------------|------|

| Power supply voltage (VDD, VID) | V+     | -0.3 | +6.5       | V    |

| Input voltage                   | VIN    | -0.3 | (V+) + 0.3 | V    |

| Input current                   | IIN    | -    | ±10        | mA   |

| Storage temperature             | TST    | -55  | +125       | °C   |

Caution) If the device is used in conditions exceeding these values, the device may be destroyed. Normal operations are not guaranteed in such extreme conditions.

# **Recommended Operating Conditions**

VSS = 0V

| Parameter             | Remark          | Symbol | Min. | Тур. | Max. | Unit |

|-----------------------|-----------------|--------|------|------|------|------|

| Operating temperature |                 | Та     | -30  |      | 85   | °C   |

| Power supply voltage  | VDD pin voltage | VDD    | 2.5  | 3.0  | 3.6  | V    |

|                       | VID pin voltage | VID    | 1.70 | 1.85 | VDD  | ٧    |

Note) When turning on VDD and VID, turn on them at the same time or turn on VDD first.

### **Electrical Characteristics**

The following condition apply unless otherwise specified: Temperature range: Tc = -30°C to 85°C

### (1) DC characteristics

| Parameter                    | Symbol | Pin        | Condition | Min.   | Тур. | Max.   | Unit |

|------------------------------|--------|------------|-----------|--------|------|--------|------|

| High level input voltage 1   | VIH1   | SI, CS     |           | 70%VID |      |        | V    |

| Low level input<br>voltage 1 | VIL1   |            |           |        |      | 30%VID | V    |

| High level input voltage 2   | VIH2   | SK<br>RSTN |           | 80%VID |      |        | V    |

| Low level input voltage 2    | VIL2   |            |           |        |      | 20%VID | V    |

| Input current                  | IIN  | SI, CS<br>SK,<br>RSTN | Vin = VSS or<br>VID                           | -10    |     | +10 | μА |

|--------------------------------|------|-----------------------|-----------------------------------------------|--------|-----|-----|----|

| High level output voltage      | VOH  | SO<br>INT             | IOH = -200μA<br>*2)                           | 90%VID |     |     | V  |

| Low level output voltage       | VOL  |                       | IOL = +200μA<br>*2)                           |        |     | 0.4 | ٧  |

| Current consumption            | IDD1 |                       | Power-down mode *1)                           |        | 0.1 | 5   | μА |

| (Total current VDD<br>and VID) | IDD2 |                       | Measurement                                   |        | 8.5 | 13  | mA |

|                                | IDD3 |                       | Mean value<br>during 100ms<br>cycle operation |        | 3.1 | 4.8 | mA |

<sup>\*1)</sup> The MCLK pin is always held "L" or "H".

## (2) AC characteristics

| Item                             | Symbol | Condition                                                                   | Min. | Тур. | Max. | Unit   |

|----------------------------------|--------|-----------------------------------------------------------------------------|------|------|------|--------|

| RSTN rising timing               | TRS    | Keep RSTN "L" time from power (VDD, VID) is ON                              | 100  |      |      | ns     |

| Measurement time                 | TSM    | From measurement mode is<br>set to INT pin rising<br>MD2 = 00H (11.2896MHz) | 37   | 38   | 39   | ms     |

| ADC resolution                   | ARS    |                                                                             |      | 8    |      | bit    |

| DAC resolution                   | DRS    |                                                                             |      | 8    |      | bit    |

| DAC step width                   | DST    | VDD = 3.0V                                                                  | 80   | 100  | 120  | μV     |

| DAC accuracy                     | DAQ    | VDD = 3.0V                                                                  |      |      | ±1/4 | LSB    |

| Sensor amplifier gain range      | SASL   | VDD = 3.0V<br>AGX, AGY, AGZ = 00H                                           | 17.7 | 18.2 | 18.7 | dB     |

|                                  | SASH   | VDD = 3.0V<br>AGX, AGY, AGZ = 1FH                                           | 27.0 | 27.5 | 28.0 | dB     |

| Sensor amplifier gain step width | AGS    |                                                                             | 0.15 | 0.3  | 0.45 | dB     |

| T-sensor<br>measurement<br>range | TOP    |                                                                             | -30  |      | 85   | °C     |

| T-sensor output code             | TOC    | VDD = 3.0V<br>Tc = 35°C                                                     | 76H  | 78H  | 7AH  | code   |

| T-sensor<br>sensitivity          | TSE    | VDD = 3.0V                                                                  | -1.4 | -1.6 | -1.8 | LSB/°C |

12/2004

<sup>\*2)</sup> Load capacitance: 20pF

| Magnetic sensor sensitivity | BSE | VDD = 2.5V ,Tc = 25°C<br>@AMP output, B = 0.6mT<br>AGX = ESNX, AGY = ESNY,<br>AGZ = ESNZ | 7.9 | 8.33 | 8.9 | mV/mT |

|-----------------------------|-----|------------------------------------------------------------------------------------------|-----|------|-----|-------|

|                             |     | AGZ = ESNZ                                                                               |     |      |     |       |

### (3) Master clock input (MCLK) characteristics

| Item                        | Symbol      | Condition                    | Min.   | Тур.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Max.   | Unit |

|-----------------------------|-------------|------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|

| Input frequency *1)         | FCLK        |                              | 11     | A September 1 - September 1 - September 2 - | 26     | MHz  |

| Clipped sine wave (T        | CXO) inpu   | t *2)                        |        | ·/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ,      |      |

| Input amplitude<br>level    | VCIN        | AC coupling                  | 0.5    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2.0    | Vp-p |

| Input impedance             | CRIN        |                              | 15     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        | kΩ   |

| Input capacitance           | CCIN        | *3)                          |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20     | pF   |

| CMOS level rectangu         | lar wave ir | nput *2)                     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | - I    |      |

| Input duty ratio            | DCLK        | Defined with 50%VID crossing | 40     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 60     | %    |

| High level input<br>voltage | CIH         |                              | 70%VID |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        | ٧    |

| Low level input voltage     | CIL         |                              |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 30%VID | ٧    |

| Input current               | CIN         | MCLK = VSS or VID            | -10    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | +10    | μА   |

- \*1) The input frequency is selected by D3 D0 of register MD2.

- \*2) The input waveform is selected by D7 of register MD2. When selecting the clipped sine wave input, connect a 100pF capacitor for AC coupling. When selecting the CMOS level rectangular wave input, input the clock signal directly (without AC coupling). (See the recommended external connection example below.)

- \*3) These parameter values are sample values; all values are not tested.

#### Recommended external connection example

#### (4) EEPROM characteristics

| Parameter                 | Min.                   | Max. | Unit   |

|---------------------------|------------------------|------|--------|

| EEPROM erase/write cycles | 1000                   |      | cycles |

| EEPROM data retention     | 2 (@85°C) + 11 (@65°C) |      | years  |

|                           | 7.7 (@75°C)            |      |        |

## Operation Overview

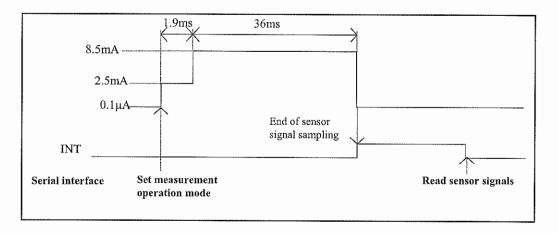

#### [Sensor signal sampling]

Sensor signal sampling is started by setting operation mode register MD1 to measurement operation (D1 - D0 = "00"). In the first 1.9ms period, internal power is turned on, and analog-to-digital conversion of the temperature sensor is performed. Then, the magnetic sensors for the X, Y, and Z directions are driven in this order, and analog-to-digital conversion is performed. Upon completion of these steps, the INT pin is driven "H", which automatically places the AK8970N in power-down mode. The level change on the INT pin notifies the external controller that sensor signal sampling has finished, then the controller reads these conversion data through the serial interface. The change on the INT pin can also be detected by reading register SR3.

If the sensor integration time is 10ms, current consumption changes in time as shown below.

Note) While the INT pin is held "H", sensor signal sampling does not start even when measurement operation mode is set. Before setting measurement operation mode, check that the INT pin is "L", or perform a dummy sensor signal read to drive the INT pin "L".

#### [Interrupt function]

The AK8970N provides an interrupt function to post the end of sensor signal conversion to the outside by changing the INT pin status from "L" to "H". The contents of SR1 or SR2 are read through the serial interface, and the INT pin is driven "L" again in synchronization with the falling edge of the 8th bit on the SK pin that determines an address. The INT pin status is reflected also in the B0 bit of register SR3.

#### [Master clock selection]

The AK8970N operates on the master clock applied to the MCLK pin. As the input waveform of the master clock, the clipped sine wave or CMOS level rectangular wave can be selected by D7 of register MD2. The master clock frequency is selected by D3 to D0 of register MD2.

#### [Setting of the integrator operation time]

The AK8970N allows the integrator operation time to be set to 10ms or 20ms separately for the X, Y, and Z direction sensors. When 20ms is set for a sensor, its sensor gain appears to be twice the gain for 10ms. The integrator operation times are set by D6 to D4 of register MD2.

Changing the integrator operation time changes the measurement time. When the operation times for the X, Y, and Z directions are all set to 20ms, the measurement time is 72.9ms (when MCLK frequency is 11.2896MHz).

<u>MS-0370-E-00</u> - 8 - 12/2004

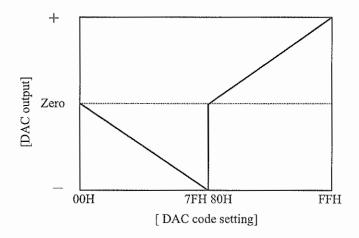

[Setting of D/A converter]

In clean magnetic environment (no offset magnetic field), AK8970N can detect terrestrial magnetism at initial value (DAX=DAY=DAZ=00H) of D/A converter.

The other hand, in strong offset field, signal level of sensor output may be beyond the input range of the A/D converter. In such case, adding the output of D/A converter to sensor signal, this signal can be regularized to the A/D converter input range.

In applications, D/A converter setting procedure is performed by the external controller, using appropriate software supplied by ASAHI-KASEI.

MS-0370-E-00 - 9 - 12/2004

[Setting of operation mode and read of conversion data]

The AK8970N transfers data to and from an external device through the serial interface described later.

The first 8 bits of serial data are decoded as an address, and only when the decoded address matches one of the 13 addresses listed in Table 1 below, a write or read operation is performed.

|      | a projection of Pilliams and their divide and debuglion observable. |                                    | Number of | Read/ |                                                                                |

|------|---------------------------------------------------------------------|------------------------------------|-----------|-------|--------------------------------------------------------------------------------|

| Name | Address                                                             | Usage                              | SK bits   | Write | Description                                                                    |

| SR1  | F0H                                                                 | Sensor signal output 1             | 24        | Read  | Output of X and Y direction signals                                            |

| SR2  | F1H                                                                 | Sensor signal output 2             | 24        | Read  | Output of Z direction and temperature sensor signals                           |

| SR3  | F2H                                                                 | Status register output             | 16        | Read  | Interrupt status and<br>EEPROM data read/write<br>mode checking                |

| MD1  | F3H                                                                 | Operation mode setting 1           | 16        | Write | Operation mode setting and<br>EEPROM read/write mode<br>setting                |

| MD2  | F4H                                                                 | Operation mode setting 2           | 16        | Write | Selection of master clock frequency & wave form, and integrator operation time |

| DAX  | F5H                                                                 | X direction sensor DAC setting     | 16        | Write | DAC setting for X direction offset compensation                                |

| DAY  | F6H                                                                 | Y direction sensor DAC setting     | 16        | Write | DAC setting for Y direction offset compensation                                |

| DAZ  | F7H                                                                 | Z direction sensor DAC setting     | 16        | Write | DAC setting for Z direction offset compensation                                |

| AGX  | F8H                                                                 | X direction sensor gain setting    | 16        | Write | Gain setting for X direction<br>sensor<br>Transcribe ESNX data of<br>EEPROM    |

| AGY  | F9H                                                                 | Y direction sensor gain setting    | 16        | Write | Gain setting for Y direction sensor Transcribe ESNY data of EEPROM             |

| AGZ  | FAH                                                                 | Z direction sensor gain<br>setting | 16        | Write | Gain setting for Z direction<br>sensor<br>Transcribe ESNZ data of<br>EEPROM    |

| TS1  | 5DH                                                                 | Test mode for factory              | 16        | Write | Normally, not used by the                                                      |

| TS2  | 5EH                                                                 | testing                            | 16        | Write | user                                                                           |

Table 1

At addresses other than the above addresses and addresses assigned to the EEPROM described later, the AK8970N does not operate. Therefore, other addresses can be assigned for controlling other devices.

## Serial Interface

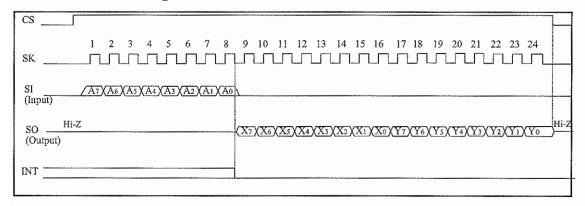

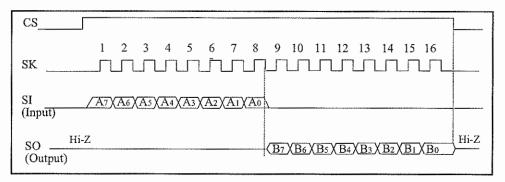

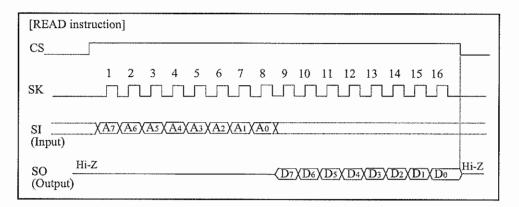

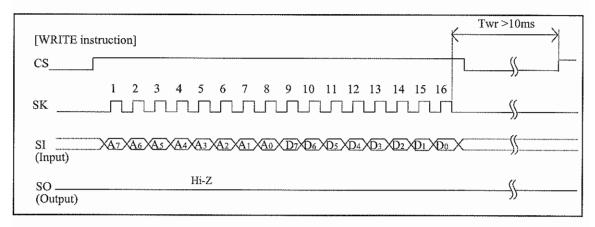

AK8970N reads and writes data through a synchronous four-wire serial interface consisting of SK, SI, SO, and CS.

When setting data is written, serial clock pulses for 16 bits are received from the SK pin, and the first 8 bits are processed as an address, and the latter 8 bits are processed as data. If the address is from F3H to FAH, the AK8970N is regarded as being selected, so the AK8970N inputs the latter 8 bits as the setting data and performs subsequent operations accordingly.

When conversion data is read from SR1 or SR2, serial clock pulses for 24 bits are received from the SK pin. If the first 8 bits indicate address F0H or F1H, two types of 8-bit sensor data are output from the SO pin starting with the MSB.

When the contents of status register SR3 are read, serial clock pulses for 16 bits are received from the SK pin, and if the first 8 bits indicate address F2H, 8-bit data is output from the SO pin starting with the MSB.

Addresses 5DH and 5EH are used for setting test mode for the AK8970N. During normal use, these addresses must not be accessed.

For addresses other than the addresses mentioned above and addresses assigned to the EEPROM, the AK8970N is regarded as not being selected, and the SO pin is held high-impedance, and no input data is supplied from the SI pin.

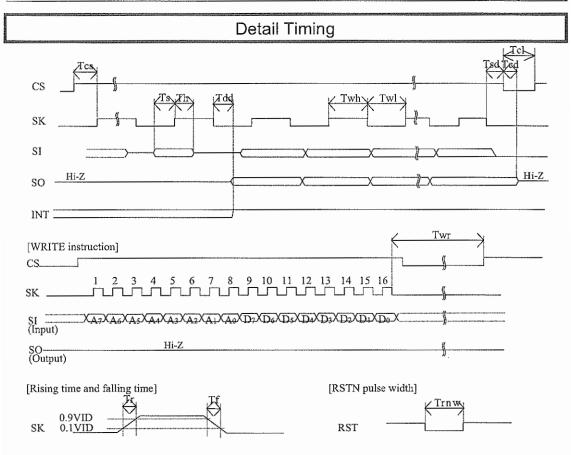

#### [Serial interface timing]

#### Write timing

#### Conversion data read timing

MS-0370-E-00 - 11 - 12/2004

Status register read timing

[Write data]

Table 2 lists the structures of setting register data input from SI.

| Register name | Address | Data name | Usage                                                 | Number of bits | Description                                                                  |

|---------------|---------|-----------|-------------------------------------------------------|----------------|------------------------------------------------------------------------------|

| MD1           | F3H     | D1 - D0   | Operation mode setting                                | 2              | 00: Measurement operation 01: Test mode                                      |

|               |         | D7 - D2   | EEPROM data<br>read/write mode<br>setting             | 6              | 101010: Write mode<br>Other than above:<br>Read mode<br>(write<br>protected) |

| MD2           | F4H     | D3 - D0   | Master clock setting                                  | 4              | See Table 3.                                                                 |

|               |         | D4        | Integration time setting for X direction sensor       | 1              | 0: 10ms<br>1: 20ms                                                           |

|               |         | D5        | Integration time<br>setting for Y<br>direction sensor | 1              |                                                                              |

|               |         | D6        | Integration time<br>setting for Z<br>direction sensor | 1              |                                                                              |

|               |         | D7        | Master clock input waveform selection                 | 1              | Clipped sine wave     CMOS level     rectangular wave                        |

| DAX           | F5H     | D7 - D0   | X direction sensor DAC setting                        | 8              | FFH: Maximum value<br>80H: 0                                                 |

| DAY           | F6H     | D7 - D0   | Y direction sensor DAC setting                        | 8              | 00H: 0<br>7FH: Minimum value                                                 |

| DAZ           | F7H     | D7 - D0   | Z direction sensor<br>DAC setting                     | 8              |                                                                              |

| AGX           | F8H     | D4 - D0   | X direction sensor gain setting                       | 5              | See Table 4.                                                                 |

| AGY           | F9H     | D4 - D0   | Y direction sensor gain setting                       | 5              | A COLOR                                                                      |

| AGZ           | FAH     | D4 - D0   | Z direction sensor gain setting                       | 5              |                                                                              |

Table 2

12/2004

| MOD data<br>D3 - D0 | Master clock<br>frequency | Measurement<br>time |  |

|---------------------|---------------------------|---------------------|--|

| 0000                | 11.2896MHz                | 38.1ms              |  |

| 0001                | 12MHz                     | 35.8ms              |  |

| 0010                | 12.288MHz                 | 35.0ms              |  |

| 0011                | 12.6MHz                   | 34.1ms              |  |

| 0100                | 13MHz                     | 33.1ms              |  |

| 0101                | 14.4MHz                   | 29.9ms              |  |

| 0110                | 15.36MHz                  | 28.0ms              |  |

| 0111                | 16.8MHz                   | 38.4ms              |  |

| 1000                | 18MHz                     | 35.8ms              |  |

| 1001                | 19.2MHz                   | 33.6ms              |  |

| 1010                | 19.68MHz                  | 32.8ms              |  |

| 1011                | 19.8MHz                   | 32.6ms              |  |

| 11XX                | 26MHz                     | 33.1ms              |  |

Table 3

| AGX, AGY,<br>AGZ data<br>D4 - D0 | Gain (dB) |

|----------------------------------|-----------|

| 00000                            | 18.2      |

| 00001                            | 18.5      |

| ••••                             | ••••      |

| 01111                            | 22.7      |

| 10000                            | 23.0      |

| 10001                            | 23.3      |

| ••••                             | ••••      |

| 11110                            | 27.2      |

| 11111                            | 27.5      |

When the value of AGX, AGY, or AGZ is N, the gain is set to  $(18.2 \pm 0.3 \times N) dB$ .

Table 4

### [Read data]

Table 5 lists the read data output from SO.

| Register name | Address | Data name | Usage                                           | Number<br>of bits | Description                                                                                 |

|---------------|---------|-----------|-------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------|

| SR1           | SR1 F0H |           | X direction data                                | 8                 | Minimum value: 00H<br>Maximum value: FFH                                                    |

|               |         | Y7 - Y0   | Y direction data                                | 8                 | Minimum value: 00H<br>Maximum value: FFH                                                    |

| SR2           | F1H     | X7 - X0   | Z direction data                                | 8                 | Minimum value: 00H<br>Maximum value: FFH                                                    |

|               |         | Y7 - Y0   | Temperature<br>sensor data                      | 8                 | 80H (typ.) for 30°C<br>As the temperature<br>increases, the data value<br>becomes smaller.  |

| SR3           | F2H     | во        | INT:<br>Interrupt status                        | 1                 | This bit shows the same state as the INT pin.  0: Interrupt reset state  1: Interrupt state |

|               |         | B1        | WRN:<br>EEPROM data<br>read/write<br>mode check | 1                 | This bit is set by the D7 - D2 bits of MD2. 0: Read mode (write protected) 1: Write mode    |

|               |         |           | Not used                                        | 6                 | Not used                                                                                    |

Table 5

## [Initial values]

When RSTN goes "L", the registers of the AK89780N are initialized, and power-down mode is entered. Table 6 lists the initial values of the registers.

| Register name | Address | Initial value | Status                                              |  |  |

|---------------|---------|---------------|-----------------------------------------------------|--|--|

| SR1           | FOH     | X7 - X0 = 00H | Minimum value                                       |  |  |

| SR2           | F1H     | Y7 - Y0 = 00H |                                                     |  |  |

| SR3           | F2H     | B1 - B0 = 00B | Interrupt reset, EEPROM read mode (write protected) |  |  |

| MD1           | F3H     | D7 - D0 = 03H | Power-down mode, EEPROM read mode (write protected) |  |  |

| MD2           | F4H     | D7 - D0 = 00H | 11.2896MHz, 10ms, clipped sine wave                 |  |  |

| DAX           | F5H     | D7 - D0 = 00H | Center value                                        |  |  |

| DAY           | F6H     |               |                                                     |  |  |

| DAZ           | F7H     |               |                                                     |  |  |

| AGX           | F8H     | D7 - D0 = 00H | 18.2dB                                              |  |  |

| AGY           | F9H     |               |                                                     |  |  |

| AGZ           | FAH     |               |                                                     |  |  |

Table 6

## Overview of the EEPROM Function

The AK8970N includes an EEPROM consisting of 9 words by 8 bits. Each word can be read and written independently.

Before the EEPROM can be read from or written to, "10" must be set in D1 and D0 of register MD1, and the operation mode must be set to EEPROM read/write mode.

The high voltage required for write operations is generated within the device.

EEPROM read and write operations are controlled by CS, SK, SI, and SO. These pins also function as the serial interface pins.

When the CS pin level changes from low to high, data is input from the SI pin on the rising edge of the clock signal input to the SK pin, and data is output from the SO pin on the falling edge of the clock signal. Data is transferred starting with the MSB. When the CS pin is low, no data is input from the SI pin, and the SO pin is in the high-impedance state.

There are two EEPROM operation modes, read and write modes, and an 8-bit address and 8-bit data are used for these operations. Whether to perform a read operation or write operation for the EEPROM is determined by the EEPROM data read/write mode setting information written in D7 to D2 of register MD1. When an address other than the EEPROM addresses of the AK8970N is input, the AK8970N ignores the address and does not input the subsequent data. In this case, the SO pin is in the high-impedance state. To enter the next data, drive the CS pin low, then input a new instruction.

## **EEPROM Operation Description**

Before the EEPROM can be read from or written to, the operation mode must be set to EEPROM read/write mode. The EEPROM operation is determined by the EEPROM read/write mode setting. The read/write mode setting is made by writing appropriate data to D7 to D2 of register MD1. (See Table 7.)

For a correct read or write operation for the EEPROM, a wait for at least 200µs is required after the above operation.

Whether read mode or write mode is set can be checked from WRN bit B1 of status register SR3. When the power is turned on, the AK8970N enters read mode (write protected).

| Operation | D1 and D0 of<br>MD1 | D7 to D2 of<br>MD1     | Address  | Data           | Description         |

|-----------|---------------------|------------------------|----------|----------------|---------------------|

| Read      | "10"                | Other than<br>"101010" | A7 to A0 | D7 to D0 (out) | EEPROM memory read  |

| Write     | "10"                | "101010"               |          | D7 to D0 (in)  | EEPROM memory write |

Table 7

#### [Read (read sequence)]

When an EEPROM address is accessed in read mode (write protected), data in the EEPROM can be read.

To perform a read operation, change the CS pin level from low to high, then input a read address. Then, data D7 - D0 at the specified address is output from the SO pin.

When clock pulses are continuously input after 1 byte of data is read, the data at the next address is output. When clock pulses are provided further after the data at the highest address has been read, the data at the lowest address is read.

After the last bit of address A0 is input, data on SI is ignored. To end the read operation, set "11" in D1 and D0 of register MD1, and set the read mode (write protected) in the D7 to D2.

#### [Write (write sequence)]

Normally, the user does not write the EEPROM

When an EEPROM address is accessed in write mode, a write into the EEPROM can be performed.

A write operation is performed by inputting a write address and data from the SI pin after the CS pin level changes from low to high. After data input, the internal programming cycle starts on the falling edge of the 16th clock pulse on SK. After last data bit D0 has been input, the CS pin must be driven low before the next SK clock rising edge is input. If the CS goes low at other timings, no write operation takes place.

The time required for a write is indicated as the programming time. During the internal programming cycle, avoid making accesses to any valid addresses of the AK8970N including read and write operations for registers.

To continue to writing to another address, wait for the programming time (Twr), then write to the address. To c To end the write operation, wait for the programming time (Twr), then set "11" to D1 and D0 of register MD1 and read mode (write protected) to D7 to D2. If the programming time is insufficient, correct writing of the previous data is not guaranteed.

During internal programming, accessing addresses other than the valid addresses of the AK8970N is possible. In this case, the AK8970N is regarded as not being selected, so the SO pin is held high-impedance, and no input data is supplied from the SI pin.

## **EEPROM Register Map**

Table 8 shows the EEPROM register map.

|                 | Address | Data                                        | The manual Control of Paris 200 completes of Assess |                                 |

|-----------------|---------|---------------------------------------------|-----------------------------------------------------|---------------------------------|

| Name<br>A7 - A0 |         | Description                                 | Number<br>of bits                                   | Factory-set<br>value            |

| WRAL            | 1FH     | Address for writing EEPROM at a time        | 8                                                   | -                               |

| ESNX            | 23H     | Element sensitivity for X direction sensor  | 8                                                   | Separately<br>adjusted<br>value |

| ESNY            | 24H     | Element sensitivity for Y direction sensor  | 8                                                   | Separately<br>adjusted<br>value |

| ESNZ            | 25H     | Element sensitivity for Z direction sensor  | 8                                                   | Separately<br>adjusted<br>value |

| EDAX1           | 26H     | Reserved                                    | 8                                                   | Not defined                     |

| EDAY1           | 27H     | Reserved                                    | 8                                                   | Not defined                     |

| EDAZ1           | 28H     | Reserved                                    | 8                                                   | Not defined                     |

| EOFX1           | 29H     | Reserved                                    | 8                                                   | Not defined                     |

| EOFY1           | 2CH     | Reserved                                    | 8                                                   | Not defined                     |

| EOFZ1           | 2DH     | Reserved                                    | 8                                                   | Not defined                     |

| ETSN            | 2EH     | Offset correction for temperature sensor 6  |                                                     | Separately<br>adjusted<br>value |

| EVRE            | 2FH     | VREF voltage and internal frequency setting | 4                                                   | Separately<br>adjusted<br>value |

Table 8

The data in ETSN and EVRE is connected to internal registers of the AK8970N to directly control correction values.

ESNX, ESNY, and ESNZ are not connected to AK8970N internal registers directly. The sensitivities for the sensors are adjusted by reading data from ESNX, ESNY, and ESNZ and setting these values in registers AGX, AGY, and AGZ.

ETSN, EVRE, ESNX, ESNY, and ESNZ contain individual values adjusted factory-test. So, these data must not be rewritten.

WRAL is an address used for testing, so it must not be used in measurement operation. If this address is accessed, the same data is written to all EEPROM addresses except 2EH and 2FH.

At other than the above addresses, the EEPROM circuit of the AK8970N does not operate.

MS-0370-E-00 - 18 - 12/2004

| Parameter              | Symbol | Condition                               | Min. | Тур. | Max. | Unit |

|------------------------|--------|-----------------------------------------|------|------|------|------|

| CS setup time          | Tcs    |                                         | 50   |      |      | ns   |

| Data setup time        | Ts     |                                         | 50   |      |      | ns   |

| Data hold time         | Th     |                                         | 50   |      |      | ns   |

| SK high time           | Twh    | VID ≥ 2.5V                              | 100  |      |      | ns   |

| SK low time            | Twl    | 2.5V > VID ≥ 1.75V                      | 150  |      |      | ns   |

| SK setup time          | Tsd    | 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 4 | 50   |      |      | ns   |

| SK → SO delay time *1) | Tdd    |                                         | 5    |      | 50   | ns   |

| CS → SO delay time *1) | Tcd    |                                         |      |      | 50   | ns   |

| SK rising time *2)     | Tr     |                                         |      |      | 100  | ns   |

| SK falling time *2)    | Tf     |                                         |      |      | 100  | ns   |

| CS low time            | Tcl    |                                         | 200  |      |      | ns   |

| Programming time       | Twr    |                                         | 10   |      |      | ms   |

| RSTN pulse width       | Trnw   |                                         | 100  |      |      | ns   |

\*1) SO load capacitance: 20pF

\*2) These parameter values are sample values; all values are not tested.

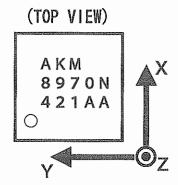

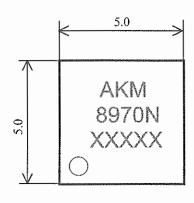

# Package

Marking

Company logo: AKM

Product name: AK8970N

Date code: X<sub>1</sub>X<sub>2</sub>X<sub>3</sub>X<sub>4</sub>X<sub>5</sub>

$X_1 = Lowest 1 digit of the year$

$X_2X_3 = Week$

$X_4$  = Alphabet assigned starting with A on a weekly basis

$X_5$  = Assembly company code

#### Pin assignments

[AK8970N]

#### Outline dimensions

Unit: mm

: Contact pin

The Outcrop area of leadframe rear face (Do not connect)

#### IMPORTANT NOTICE \_

These products and their specifications are subject to change without notice.

Before considering any use or application, consult the Asahi Kasei Microsystems Co., Ltd. (AKM) sales office or authorized distributor concerning their current status.