### 40 V, 3 A, quad power half bridge

Datasheet - production data

#### **Features**

- Multipower BCD technology

- Low input/output pulse width distortion

- 200 m $\Omega$  R<sub>dsON</sub> complementary DMOS output stage

- CMOS-compatible logic inputs

- Thermal protection

- Thermal warning output

- Undervoltage protection

- · Short-circuit protection

### **Description**

The STA515W is a monolithic quad half-bridge stage in Multipower BCD Technology. The device can be used as a dual bridge or reconfigured, by connecting pin CONFIG to pins VDD, as a single bridge with double-current capability.

The device is designed, particularly, to be the output stage of a stereo all-digital high-efficiency amplifier. It is capable of delivering 10 W x 4 channels into 4  $\Omega$  loads with 10% THD at  $V_{CC}$  = 18 V in single-ended configuration.

It can also deliver 20 W + 20 W into 8  $\Omega$  loads with 10% THD at V<sub>CC</sub> = 18 V in BTL configuration or, in single parallel BTL configuration, 40 W into a 8  $\Omega$  load with 10% THD at V<sub>CC</sub> = 26 V.

The input pins have a threshold proportional to the voltage on pin  $V_L$ .

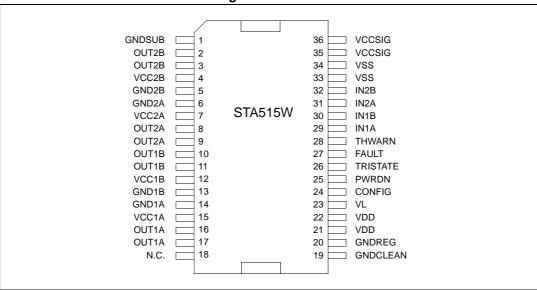

The STA515W comes in a 36-pin PowerSSO package with exposed pad down (EPD).

**Table 1. Device summary**

| Order code  | Ambient temp. range | Package        | Packaging     |  |

|-------------|---------------------|----------------|---------------|--|

| STA515W13TR | 0 to 70 °C          | PowerSSO36 EPD | Tape and reel |  |

Introduction STA515W

## 1 Introduction

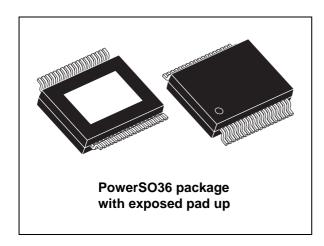

Figure 1. STA515W circuit for quad single-ended amplifiers

STA515W Pin description

## 2 Pin description

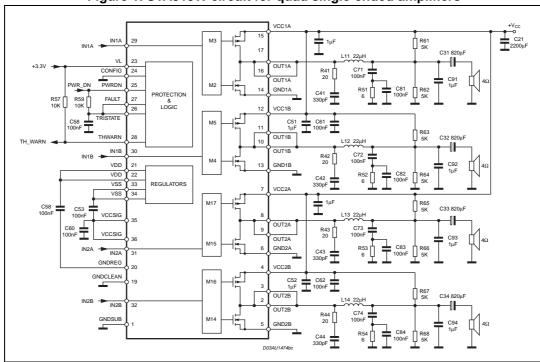

Figure 2. Pin out

Table 2. Pin list

| Pin    | Name     | Туре | Description                                        |  |

|--------|----------|------|----------------------------------------------------|--|

| 1      | GNDSUB   | PWR  | Substrate ground                                   |  |

| 2, 3   | OUT2B    | 0    | Output half bridge 2B                              |  |

| 4      | VCC2B    | PWR  | Positive supply                                    |  |

| 5      | GND2B    | PWR  | Negative supply                                    |  |

| 6      | GND2A    | PWR  | Negative supply                                    |  |

| 7      | VCC2A    | PWR  | Positive supply                                    |  |

| 8, 9   | OUT2A    | 0    | Output half bridge 2A                              |  |

| 10, 11 | OUT1B    | 0    | Output half bridge 1B                              |  |

| 12     | VCC1B    | PWR  | Positive supply                                    |  |

| 13     | GND1B    | PWR  | Negative supply                                    |  |

| 14     | GND1A    | PWR  | Negative supply                                    |  |

| 15     | VCC1A    | PWR  | Positive supply                                    |  |

| 16, 17 | OUT1A    | 0    | Output half bridge 1A                              |  |

| 18     | N.C.     | -    | No internal connection                             |  |

| 19     | GNDCLEAN | PWR  | Logical ground                                     |  |

| 20     | GNDREG   | PWR  | Ground for regulator V <sub>DD</sub>               |  |

| 21, 22 | VDD      | PWR  | 5-V regulator referred to ground                   |  |

| 23     | VL       | PWR  | High logical state setting voltage, V <sub>L</sub> |  |

Pin description STA515W

Table 2. Pin list (continued)

| Pin    | Name     | Туре | Description                                                                                                                                  |

|--------|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 24     | CONFIG   | I    | Configuration pin: 0: normal operation 1: bridges in parallel, see <i>Parallel-output and high-current operation on page 10</i>              |

| 25     | PWRDN    | I    | Stand-by pin: 0: low-power mode 1: normal operation                                                                                          |

| 26     | TRISTATE | I    | Hi-Z pin: 0: all power amplifier outputs in high-impedance state 1: normal operation                                                         |

| 27     | FAULT    | 0    | Fault pin advisor (open-drain device, needs pull-up resistor): 0: fault detected (short circuit or thermal, for example) 1: normal operation |

| 28     | THWARN   | 0    | Thermal-warning advisor (open-drain device, needs pull-up resistor): 0: temperature of the IC >130 °C 1: normal operation                    |

| 29     | IN1A     | 1    | Input of half bridge 1A                                                                                                                      |

| 30     | IN1B     | I    | Input of half bridge 1B                                                                                                                      |

| 31     | IN2A     | 1    | Input of half bridge 2A                                                                                                                      |

| 32     | IN2B     | 1    | Input of half bridge 2B                                                                                                                      |

| 33, 34 | VSS      | PWR  | 5-V regulator referred to +V <sub>CC</sub>                                                                                                   |

| 35, 36 | VCCSIG   | PWR  | Signal positive supply                                                                                                                       |

### 3 Electrical characteristics

Table 3. Absolute maximum ratings

| Symbol                            | Parameter                             | Value      | Unit |

|-----------------------------------|---------------------------------------|------------|------|

| $V_{CC}$                          | DC supply voltage (Pins 4, 7, 12, 15) | 40         | V    |

| V <sub>max</sub>                  | Maximum voltage on pins 23 to 32      | 5.5        | V    |

| T <sub>op</sub>                   | Operating temperature range           | 0 to 70    | °C   |

| P <sub>tot</sub>                  | Power dissipation (Tcase = 70 °C)     | 21         | W    |

| T <sub>stg</sub> , T <sub>j</sub> | Storage and junction temperature      | -40 to 150 | °C   |

Table 4. Recommended operating conditions

| Symbol           | Parameter                             | Min | Тур | Max | Unit |

|------------------|---------------------------------------|-----|-----|-----|------|

| V <sub>CC</sub>  | DC supply voltage (Pins 4, 7, 12, 15) | 10  | -   | 36  | V    |

| $V_L$            | Input logic reference                 | 2.7 | 3.3 | 5.0 | ٧    |

| T <sub>amb</sub> | Ambient temperature                   | 0   | -   | 70  | °C   |

Table 5. Thermal data

| Symbol              | Parameter                                         | Min | Тур | Max | Unit |

|---------------------|---------------------------------------------------|-----|-----|-----|------|

| T <sub>j-case</sub> | Thermal resistance junction to case (thermal pad) | -   | -   | 1.5 | °C/W |

| T <sub>jSD</sub>    | Thermal shut-down junction temperature            | -   | 150 | -   | °C   |

| T <sub>warn</sub>   | Thermal warning temperature                       | -   | 130 | -   | °C   |

| t <sub>hSD</sub>    | Thermal shut-down hysteresis                      | -   | 25  | -   | °C   |

Unless otherwise stated, the test conditions for *Table 6* below are V<sub>L</sub> = 3.3 V, V<sub>CC</sub> = 30 V, R<sub>L</sub> = 8  $\Omega$ , f<sub>SW</sub> = 384 kHz and T<sub>amb</sub> = 25 °C

**Table 6. Electrical characteristics**

| Symbol            | Parameter                                             | Test conditions        | Min | Тур | Max | Unit |

|-------------------|-------------------------------------------------------|------------------------|-----|-----|-----|------|

| R <sub>dsON</sub> | Power P-channel/N-channel<br>MOSFET R <sub>dsON</sub> | I <sub>dd</sub> = 1 A  | -   | 200 | 270 | mΩ   |

| I <sub>dss</sub>  | Power P-channel/N-channel leakage Idss                | V <sub>CC</sub> = 35 V | -   | -   | 50  | μА   |

| 9 <sub>N</sub>    | Power P-channel R <sub>dsON</sub> matching            | I <sub>dd</sub> = 1 A  | 95  | -   | -   | %    |

| g <sub>P</sub>    | Power N-channel R <sub>dsON</sub> matching            | I <sub>dd</sub> = 1 A  | 95  | -   | -   | %    |

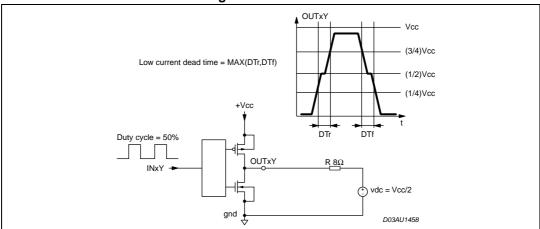

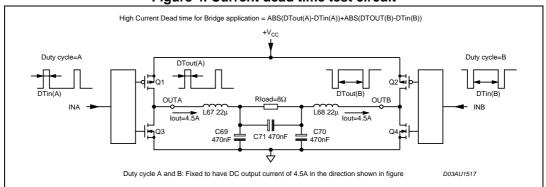

| Dt_s              | Low current dead time (static)                        | see Figure 3           | -   | 10  | 20  | ns   |

Electrical characteristics STA515W

Table 6. Electrical characteristics (continued)

| Symbol               | Parameter                                                                  | Test conditions                                                                             | Min                        | Тур | Max                            | Unit |

|----------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------|-----|--------------------------------|------|

| Dt_d                 | High current dead time (dynamic)                                           | $L = 22 \ \mu H, \ C = 470 \ nF$ $R_L = 8 \ \Omega, \ I_{dd} = 3.0 \ A$ see <i>Figure 4</i> | -                          | -   | 50                             | ns   |

| t <sub>d ON</sub>    | Turn-on delay time                                                         | Resistive load                                                                              | -                          | -   | 100                            | ns   |

| t <sub>d OFF</sub>   | Turn-off delay time                                                        | Resistive load                                                                              | -                          | -   | 100                            | ns   |

| t <sub>r</sub>       | Rise time                                                                  | Resistive load see <i>Figure 3</i>                                                          | -                          | -   | 25                             | ns   |

| t <sub>f</sub>       | Fall time                                                                  | Resistive load see <i>Figure 3</i>                                                          | -                          | -   | 25                             | ns   |

| V <sub>CC</sub>      | Supply operating voltage                                                   | -                                                                                           | 10                         | -   | 36                             | V    |

| V <sub>IN-Low</sub>  | Half-bridge input, low level voltage                                       | -                                                                                           | -                          | -   | V <sub>L</sub> / 2 -<br>300 mV | V    |

| V <sub>IN-High</sub> | Half-bridge input, high level voltage                                      | -                                                                                           | V <sub>L</sub> /2 + 300 mV | -   | -                              | V    |

| I <sub>IN-H</sub>    | High level input current                                                   | $V_{IN} = V_{L}$                                                                            | -                          | 1   | -                              | μΑ   |

| I <sub>IN-L</sub>    | Low level input current                                                    | V <sub>IN</sub> = 0.3 V                                                                     | -                          | 1   | -                              | μΑ   |

| I <sub>PWRDN-H</sub> | High level PWRDN pin input current                                         | V <sub>L</sub> = 3.3 V                                                                      | -                          | 35  | -                              | μΑ   |

| $V_{Low}$            | Low logical state voltage (pins PWRDN, TRISTATE) (see Table 7)             | V <sub>L</sub> = 3.3 V                                                                      | -                          | -   | 0.8                            | V    |

| $V_{High}$           | High logical state voltage (pins PWRDN, TRISTATE) (see <i>Table 7</i> )    | V <sub>L</sub> = 3.3 V                                                                      | 1.7                        | -   | -                              | V    |

| I <sub>VCC</sub> -   | Supply current from V <sub>CC</sub> in power down                          | V <sub>PWRDN</sub> = 0 V                                                                    | -                          | -   | 3                              | mA   |

| I <sub>FAULT</sub>   | Output current on pins<br>FAULT, THWARN with fault<br>condition            | V <sub>pin</sub> = 3.3 V                                                                    | -                          | 1   | -                              | mA   |

| I <sub>VCC-HiZ</sub> | Supply current from V <sub>CC</sub> in 3-state                             | V <sub>TRISTATE</sub> = 0 V                                                                 | -                          | 22  | -                              | mA   |

| I <sub>VCC</sub>     | Supply current from V <sub>CC</sub> in operation (both channels switching) | Input pulse width<br>= 50% duty,<br>switching frequency<br>= 384 kHz,<br>no LC filters      | -                          | 50  | -                              | mA   |

| I <sub>OCP</sub>     | Overcurrent protection threshold Isc (short circuit current limit)         | -                                                                                           | 3                          | 6   | -                              | А    |

| V <sub>UVP</sub>     | Undervoltage protection threshold                                          | -                                                                                           | -                          | 7   | -                              | V    |

| t <sub>pw_min</sub>  | Output minimum pulse width                                                 | No load                                                                                     | 70                         | -   | 150                            | ns   |

Table 7. Threshold switching voltage variation with voltage on pin VL

| Voltage on pin VL, V <sub>L</sub> | V <sub>LOW</sub> max | V <sub>HIGH</sub> min | Unit |

|-----------------------------------|----------------------|-----------------------|------|

| 2.7                               | 0.7                  | 1.5                   | V    |

| 3.3                               | 0.8                  | 1.7                   | V    |

| 5.0                               | 0.85                 | 1.85                  | V    |

Table 8. Logic truth table

| Pin      | Inputs as p | er <i>Figure 4</i> | Transistors as per Figure 4 |     |     |     | Output mode |

|----------|-------------|--------------------|-----------------------------|-----|-----|-----|-------------|

| TRISTATE | INxA        | INxB               | Q1                          | Q2  | Q3  | Q4  | Output mode |

| 0        | х           | х                  | Off                         | Off | Off | Off | Hi Z        |

| 1        | 0           | 0                  | Off                         | Off | On  | On  | Dump        |

| 1        | 0           | 1                  | Off                         | On  | On  | Off | Negative    |

| 1        | 1           | 0                  | On                          | Off | Off | On  | Positive    |

| 1        | 1           | 1                  | On                          | On  | Off | Off | Not used    |

Test circuits STA515W

### 4 Test circuits

Figure 3. Test circuit

Figure 4. Current dead time test circuit

### 5 Application information

The STA515W is a dual channel H-bridge that can deliver 20 W per channel into 8  $\Omega$  with 10% THD at  $V_{CC}$  = 18 V with high efficiency.

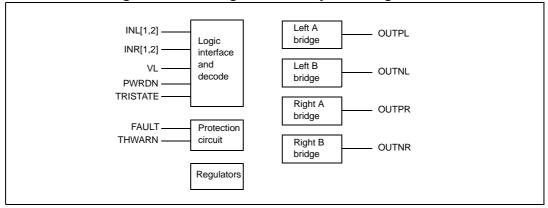

The STA515W converts both DDX and binary-logic-controlled PWM signals into audio power at the load. It includes a logic interface, integrated bridge drivers, high efficiency MOSFET outputs and thermal and short-circuit protection circuitry.

In DDX mode, two logic-level signals per channel are used to control the high-speed MOSFET switches which drive the speaker load in a bridge configuration, according to the damped ternary modulation operation.

In binary mode, both full-bridge and half-bridge modes are supported.

The STA515W includes overcurrent and thermal protection as well as an undervoltage lockout with automatic recovery. A thermal warning status is also provided.

INL[1,2] - OUTPL Left Logic INR[1,2] H-bridge interface OUTNL and decode **PWRDN TRISTATE** OUTPR Right H-bridge **FAULT** Protection OUTNR THWARN circuit Regulators

Figure 5. Block diagram for DDX or binary modes

Figure 6. Block diagram for binary half-bridge mode

#### Logic interface and decode

The STA515W power outputs are controlled using one or two logic-level timing signals. In order to provide a proper logic interface, pin VL must operate at the same voltage as the DDX control logic supply.

#### **Protection circuits**

The STA515W includes protection circuitry for overcurrent and thermal overload conditions. A thermal warning pin (THWARN) is activated low (open-drain MOSFET) when the IC temperature exceeds 130 °C, which is in advance of the thermal shutdown protection. When a fault condition is detected an internal fault signal acts to immediately disable the output power MOSFETs, placing both H-bridges in the high-impedance state. At the same time an open-drain MOSFET connected to pin FAULT is switched on.

There are two possible modes subsequent to activating a fault:

- Shutdown mode:

- with pins FAULT (with pull-up resistor) and TRISTATE independent, an activated fault disables the device, signalling low at pin FAULT.

- The device may subsequently be reset to normal operation by toggling pin TRISTATE from high to low and back to high using an external logic signal.

- Automatic recovery mode:

- This is shown in the applications circuit in *Figure 7* and *Figure 7* on page 11. Pins FAULT and TRISTATE are shorted together and connected to a time constant circuit comprising R59 and C58.

- An activated fault forces a reset on pin TRISTATE causing normal operation to resume following a delay determined by the time constant of the circuit.

- If the fault condition is still present, the circuit operation continues, repeating until the fault condition is removed.

- An increase in the time constant of the circuit produces a longer recovery interval.

Care must be taken in the overall system design so as not to exceed the protection thresholds under normal operation.

#### **Power outputs**

The STA515W power and output pins are duplicated to provide a low-impedance path for the device bridged outputs. All duplicated power, ground and output pins must be connected for proper operation.

Pins PWRDN or TRISTATE should be used to set all MOSFETS to the high-impedance state during power-up and until the logic power supply, VL, has settled.

#### Parallel-output and high-current operation

When using DDX mode, the STA515W outputs can be connected in parallel to increase the output current capability. In this configuration the device can provide 40 W into 8  $\Omega$ .

This mode of operation is enabled with pin CONFIG connected to VDD. The inputs must be combined to give INLA = INLB and INRA = INRB, then the corresponding outputs can be shorted together to give OUTLA = OUTLB and OUTRA = OUTRB.

#### **Output filter**

A passive 2nd-order filter is used on the STA515W power outputs to reconstruct an analog audio signal. The system performance can be significantly affected by the output filter design and choice of passive components.

Filter designs for  $4-\Omega$  and  $8-\Omega$  loads are shown in the applications circuits of *Figure 1 on page 2* for the half-bridge mode, and *Figure 7* and *Figure 8 on page 11* for the full bridge.

10/16 DocID11079 Rev 3

#### **Applications circuits**

Figure 7 below shows a typical full-bridge circuit for supplying 20 W + 20 W into 8  $\Omega$ speakers with 10% THD at  $V_{CC}$  = 18 V.

Figure 7. Typical stereo full-bridge configuration for 20 + 20 W \_\_\_\_\_C55 1000μF VL CONFIG OUT1A M2 & LOGIC M5 C31 220nF OUT1B 10 IN1B OUT1B IN1B M4 VDD VDD 22 VSS 33 REGULATORS M17 C32 220nF L113 22μH OUT2A OUT2A M15 GND2A IN2/ C108 470nF GNDREG VCC2B C106 100nF M16 OUT2B OUT2B L112 22µF D00AU1148Bb

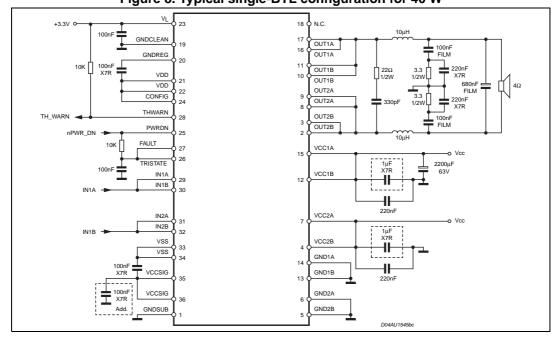

Figure 8 below shows a single-BTL configuration capable of supplying 40 W into a 4  $\Omega$  load at 10% THD with  $V_{CC}$  = 19 V. This result was obtained with peak power for <1 s using the STA308+STA515W+STA50X demo board. A PWM modulator as driver is required.

Figure 8. Typical single-BTL configuration for 40 W

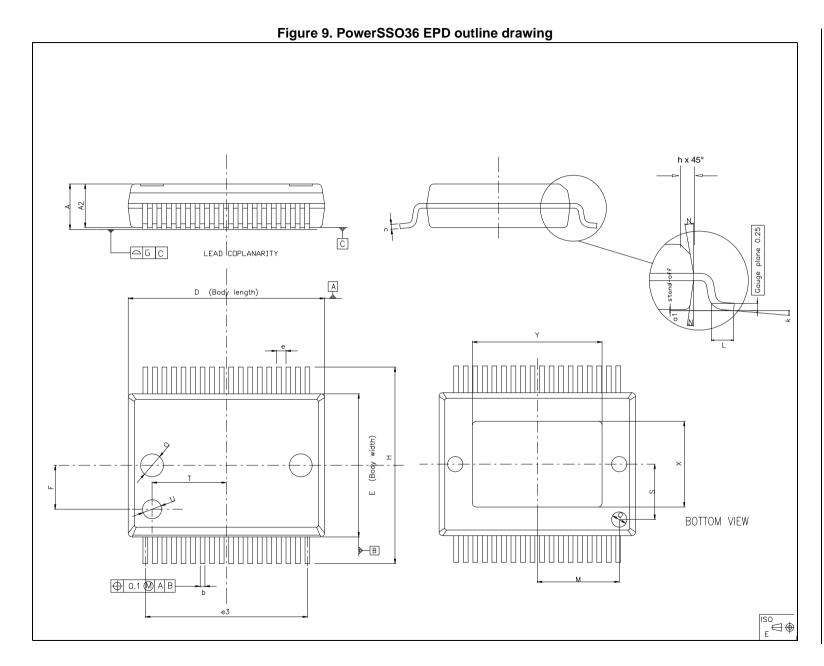

## 6 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

The STA515W comes in a 36-pin PowerSSO package with exposed pad down (EPD).

Figure 9 below shows the package outline and Table 9 gives the dimensions.

12/16 DocID11079 Rev 3

Table 9. PowerSSO36 EPD dimensions

|        |       | Dimensions in mm |            |       | Dimensions in inches |            |  |  |

|--------|-------|------------------|------------|-------|----------------------|------------|--|--|

| Symbol | Min   | Тур              | Max        | Min   | Тур                  | Max        |  |  |

| Α      | 2.15  | -                | 2.47       | 0.085 | -                    | 0.097      |  |  |

| A2     | 2.15  | -                | 2.40       | 0.085 | -                    | 0.094      |  |  |

| a1     | 0.00  | -                | 0.10       | 0.000 | -                    | 0.004      |  |  |

| b      | 0.18  | -                | 0.36       | 0.007 | -                    | 0.014      |  |  |

| С      | 0.23  | -                | 0.32       | 0.009 | -                    | 0.013      |  |  |

| D      | 10.10 | -                | 10.50      | 0.398 | -                    | 0.413      |  |  |

| E      | 7.40  | -                | 7.60       | 0.291 | -                    | 0.299      |  |  |

| е      | -     | 0.5              | -          | -     | 0.020                | -          |  |  |

| e3     | -     | 8.5              | -          | -     | 0.335                | -          |  |  |

| F      | -     | 2.3              | -          | -     | 0.091                | -          |  |  |

| G      | -     | -                | 0.10       | -     | -                    | 0.004      |  |  |

| Н      | 10.10 | -                | 10.50      | 0.398 | -                    | 0.413      |  |  |

| h      | -     | -                | 0.40       | -     | -                    | 0.016      |  |  |

| k      | 0     | -                | 8 degrees  | 0     | -                    | 8 degrees  |  |  |

| L      | 0.60  | -                | 1.00       | 0.024 | -                    | 0.039      |  |  |

| М      | -     | 4.30             | -          | -     | 0.169                | -          |  |  |

| N      | -     | -                | 10 degrees | -     | -                    | 10 degrees |  |  |

| 0      | -     | 1.20             | -          | -     | 0.047                | -          |  |  |

| Q      | -     | 0.80             | -          | -     | 0.031                | -          |  |  |

| S      | -     | 2.90             | -          | -     | 0.114                | -          |  |  |

| Т      | -     | 3.65             | -          | -     | 0.144                | -          |  |  |

| U      | -     | 1.00             | -          | -     | 0.039                | -          |  |  |

| Х      | 4.10  | -                | 4.70       | 0.161 | -                    | 0.185      |  |  |

| Υ      | 6.50  | -                | 7.10       | 0.256 | -                    | 0.280      |  |  |

14/16 DocID11079 Rev 3

STA515W Revision history

# 7 Revision history

Table 10. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                          |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Nov-2004    | 1        | Initial release.                                                                                                                                                                                                                                                                                                                 |

| 27-Apr-2010 | 2        | Added order code STA515W13TR  Modified Figure 1 on page 2  Reconstructed pin list in Table 2 on page 3 with information from former table 3 Functional pin status  Updated Vlow and Vhigh spec in Table 6 on page 5  Modified Figure 3 and Figure 4 on page 8  Updated applications circuits in Figure 7 and Figure 8 on page 11 |

| 24-Feb-2014 | 3        | Updated order code Table 1 on page 1                                                                                                                                                                                                                                                                                             |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries. Information in this document supersedes and replaces all information previously supplied. The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2014 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

16/16 DocID11079 Rev 3

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

STMicroelectronics: STA515W13TR