# - NEW PRODUCT INTRODUCTION -EP1810GC-35

Rochester Electronics has re-introduced and continues to manufacture critically needed semiconductors with the full authorization of the original manufacturer and an attention to quality that meets or exceeds the original component.

Original Manufacturer:

# Re-introduced by Rochester Electronics on **January, 12, 2012**

# EP1810GC-35

Original Part Number: **EP1810GC-35** Description: **Complex EPLD** Package: **68 pin PGA** Manufacturing Flow: **Commercial** Manufacturing Type: **Rochester re-creation device**

## **Related Devices**

[ by temperature / package type / speed / application ]

EP1810GI-35 EP1810GM/B EP1810LC-45 EP1800ILC-70

EP1810LC-45AA EP1810LC-45H EP1810LI-45

# HIGH PERFORMANCE COMPLEX EPLD featuring up to 64 inputs and 48 outputs

EP1810 devices offer LSI density, TTL-equivalent speed, and low power consumption. EP1810 devices have 48 macrocells, 16 dedicated input pins, and 48 I/O pins. EP1810 devices are divided into four quadrants, each containing 12 macrocells. Of the 12 macrocells in each quadrant, 8 have quadrant feedback and are "local" macrocells. The remaining 4 macrocells in the quadrant are "global" macrocells. Both local and global macrocells can access

signals from the global bus, which consists of the true and complement forms of the dedicated inputs and the true and complement forms of the feedbacks from the global macrocells.

#### Worldwide Corporate Headquarters 16 Malcolm Hoyt Drive . Newburyport, MA 01950

**S** *phone* 978.462.9332 . *email* sales@rocelec.com . *web* www.rocelec.com

© Rochester Electronics, LLC - All Rights Reserved - 11162012

#### ALTERA CORP

# EP1810 EPLD

#### Features

- □ High-performance, 48-macrocell Classic EPLD

- Combinatorial speeds with  $t_{PD} = 20, 25, 35, and 45 ns$

- Counter frequencies up to 50 MHz

- Pipelined data rates up to 62.5 MHz

- Programmable I/O architecture with up to 64 inputs or 48 outputs

- Pin-, function-, and programming file-compatible with Altera's EP1810T and EP1810 MIL-STD-883-compliant devices

- D Programmable Clock option for independent clocking of all registers

- Macrocells individually programmable as D, T, JK, or SR flipflops, or for combinatorial operation

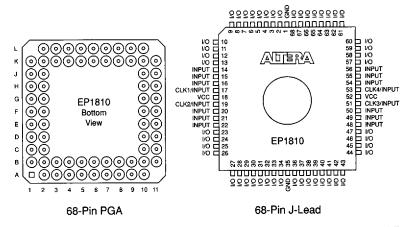

- Available in 68-pin windowed ceramic and one-time-programmable plastic packages (see Figure 28):

- Pin-grid array package (ceramic PGA only)

- J-lead chip carrier (JLCC and PLCC)

#### Figure 28. EP1810 Package Pin-Out Diagrams

Package outlines not drawn to scale. See Table 2 in this data sheet for PGA package pin-out information. Windows in ceramic packages only.

## General Description

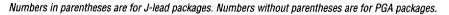

The Altera EP1810 EPLD offers LSI density, TTL-equivalent speed, and low power consumption. The EP1810 has 48 macrocells, 16 dedicated input pins, and 48 I/O pins (see Figure 29). The EP1810 is divided into four quadrants, each containing 12 macrocells. Of the twelve macrocells in each quadrant, 8 have quadrant feedback and are "local" macrocells. (See "Feedback Selection" earlier in this data sheet for more information.) The remaining 4 macrocells in the quadrant are "global" macrocells. Both local and global macrocells can access signals from the global bus, which consists

Data Sheet

#### EP1810 EPLD

#### Figure 29. EP1810 Block Diagram

of the true and complement forms of the dedicated inputs and the true and complement forms of the feedbacks from the global macrocells.

The EP1810 also has four dedicated inputs (one in each quadrant) that can be used as quadrant Clock inputs. If the dedicated input is used as a Clock pin, the input feeds the Clock input of all registers in that particular quadrant.

#### ALTERA CORP

#### **Data Sheet**

#### EP1810 EPLD

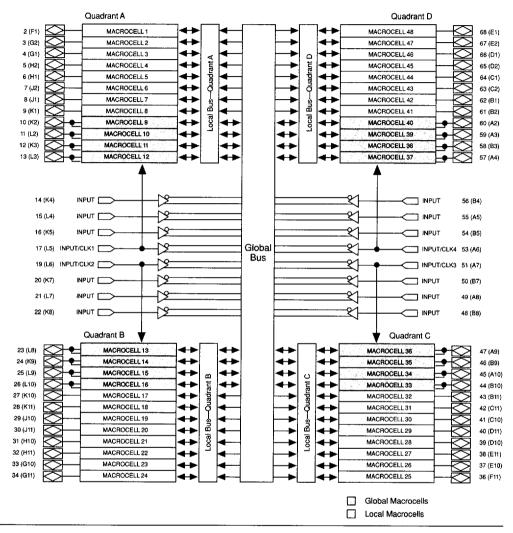

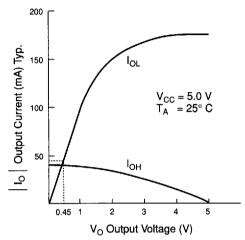

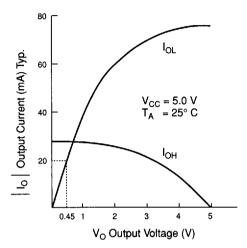

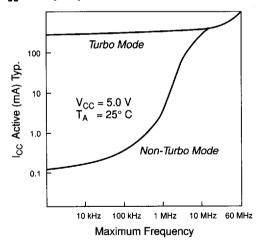

Figure 30 shows the output drive characteristics of EP1810 I/O pins and typical supply current ( $I_{CC}$ ) versus frequency for the EP1810 EPLDs.

#### Figure 30. EP1810 Maximum Output Drive Characteristics & I<sub>CC</sub> vs. Frequency

Output Drive Characteristics of EP1810-35 & EP1810-45 EPLDs

ICC vs. Frequency of EP1810 EPLDs

Data Sheet

Absolute Maximum Rating See Operating Requirements for Altera Devices in this data book.

| Symbol           | Parameter                         | Conditions          | Min  | Max  | Unit |

|------------------|-----------------------------------|---------------------|------|------|------|

| v <sub>cc</sub>  | Supply voltage                    | With respect to GND | 2.0  | 7.0  | v    |

| V <sub>PP</sub>  | Programming supply voltage        | Note (1)            | -2.0 | 13.5 | v    |

| V <sub>I</sub>   | DC input voltage                  |                     | -2.0 | 7.0  | V    |

| IMAX             | DC V <sub>CC</sub> or GND current |                     | -300 | 300  | mA   |

| LOUT             | DC output current, per pin        |                     | -25  | 25   | mA   |

| PD               | Power dissipation                 |                     |      | 1500 | mW   |

| T <sub>STG</sub> | Storage temperature               | No bias             | -65  | 150  | °C   |

| T <sub>AMB</sub> | Ambient temperature               | Under bias          | -65  | 135  | °C   |

#### **Recommended Operating Conditions** Note (2)

| Symbol Parameter |                       | Conditions         | Min        | Max             | Unit |

|------------------|-----------------------|--------------------|------------|-----------------|------|

| V <sub>CC</sub>  | Supply voltage        |                    | 4.75 (4.5) | 5.25 (5.5)      | v    |

| V,               | Input voltage         |                    | 0          | V <sub>CC</sub> | V    |

| ٧ <sub>0</sub>   | Output voltage        |                    | 0          | V <sub>CC</sub> | v    |

| Τ <sub>Α</sub>   | Operating temperature | For commercial use | 0          | 70              | °C   |

| Τ <sub>Α</sub>   | Operating temperature | For industrial use | -40        | 85              | °C   |

| т <sub>с</sub>   | Case temperature      | For military use   | -55        | 125             | °C   |

| t <sub>R</sub>   | Input rise time       | Note (3)           |            | 50              | ns   |

| t <sub>F</sub>   | Input fall time       | -                  |            | 50              | ns   |

#### DC Operating Conditions Note (2), (4), (5)

| Symbol           | Parameter                          | Conditions                                        | Speed<br>Grade | Min  | Тур | Max                   | Unit |

|------------------|------------------------------------|---------------------------------------------------|----------------|------|-----|-----------------------|------|

| V <sub>IH</sub>  | High-level input voltage           |                                                   |                | 2.0  |     | V <sub>CC</sub> + 0.3 | v    |

| V <sub>IL</sub>  | Low-level input voltage            |                                                   |                | 0.3  |     | 0.8                   | ٧    |

| v <sub>он</sub>  | High-level TTL output voltage      | $I_{OH} = -4 \text{ mA DC}$                       |                | 2.4  |     |                       | v    |

| V <sub>он</sub>  | High-level CMOS output voltage     | 1 <sub>OH</sub> = -2 mA DC                        |                | 3.84 |     |                       | ٧    |

| V <sub>OL</sub>  | Low-level output voltage           | I <sub>OL</sub> = 4 mA DC                         |                |      |     | 0.45                  | v    |

| l <sub>i</sub>   | Input leakage current              | V <sub>1</sub> = V <sub>CC</sub> or GND           |                | -10  |     | 10                    | μA   |

| loz              | Tri-state output off-state current | $V_0 = V_{CC} \text{ or GND}$                     |                | -10  |     | 10                    | μA   |

| I <sub>CC1</sub> | V <sub>CC</sub> supply current     | $V_{I} = V_{CC} \text{ or GND, } I_{O} = 0,$      | -20, -25       |      | 50  | 150                   | μA   |

|                  | (non-turbo, standby)               | Notes (6), (7)                                    | -35, -45       |      | 35  | 150                   | μA   |

| I <sub>CC2</sub> | V <sub>CC</sub> supply current     | V <sub>I</sub> = V <sub>CC</sub> or GND, No load, | -20, -25       |      | 20  | 40                    | mA   |

|                  | (non-turbo, active)                | f = 1.0 MHz, Note (7)                             | -35, -45       |      | 10  | 30 (40)               | mΑ   |

| I <sub>CC3</sub> | V <sub>CC</sub> supply current     | V <sub>1</sub> = V <sub>CC</sub> or GND, No load, | -20, -25       |      | 180 | 225 (250)             | mA   |

|                  | (turbo, active)                    | f = 1.0 MHz, <i>Note (7)</i>                      | -35, -45       |      | 100 | 180 (240)             | mA   |

#### Data Sheet

Capacitance Note (8)

| Symbol | Parameter             | Conditions                   |  | Max | Unit |

|--------|-----------------------|------------------------------|--|-----|------|

| CIN    | Input capacitance     | $V_{1N} = 0 V, f = 1.0 MHz$  |  | 20  | ρF   |

| COUT   | Output capacitance    | $V_{OUT} = 0 V, f = 1.0 MHz$ |  | 20  | pF   |

| CCLK   | Clock pin capacitance | $V_{1N} = 0 V$ , f = 1.0 MHz |  | 25  | рF   |

#### AC Operating Conditions: EP1810-20, EP1810-25 Note (5)

| External Timing Parameters |                                    |            | EP18 | EP1810-20 |     | 10-25 | Non-Turbo<br>Adder |      |

|----------------------------|------------------------------------|------------|------|-----------|-----|-------|--------------------|------|

| Symbol                     | Parameter                          | Conditions | Min  | Max       | Min | Max   | Note (9)           | Unit |

| t <sub>PD1</sub>           | Input to non-registered output     | C1 = 35 pF |      | 20        |     | 25    | 25                 | ns   |

| t <sub>PD2</sub>           | I/O input to non-registered output |            |      | 22        |     | 28    | 25                 | ns   |

| t <sub>su</sub>            | Global clock setup time            |            | 13   |           | 17  |       | 25                 | ns   |

| t <sub>H</sub>             | Global clock hold time             |            | 0    |           | 0   |       | 0                  | ns   |

| t <sub>co1</sub>           | Global clock to output delay       | C1 = 35 pF |      | 15        |     | 18    | 0                  | ns   |

| t <sub>CH</sub>            | Global clock high time             |            | 8    |           | 10  |       | 0                  | ns   |

| t <sub>CL</sub>            | Global clock low time              |            | 8    |           | 10  |       | 0                  | ns   |

| t <sub>ASU</sub>           | Array clock setup time             |            | 8    |           | 10  |       | 25                 | ns   |

| t <sub>AH</sub>            | Array clock hold time              |            | 8    |           | 10  |       | 0                  | ns   |

| t <sub>ACO1</sub>          | Array clock to output delay        | C1 = 35 pF |      | 20        |     | 25    | 25                 | ns   |

| t <sub>CNT</sub>           | Minimum global clock period        |            |      | 20        |     | 25    | 0                  | ns   |

| f <sub>CNT</sub>           | Maximum internal frequency         | Note (7)   | 50   |           | 40  |       | 0                  | MHz  |

| f <sub>MAX</sub>           | Maximum clock frequency            | Note (10)  | 62.5 |           | 50  |       | 0                  | MHz  |

| Internal Timing Parameters |                                |                      | EP1810-20 |     | EP1810-25 |     | Non-Turbo<br>Adder |      |

|----------------------------|--------------------------------|----------------------|-----------|-----|-----------|-----|--------------------|------|

| Symbol                     | Parameter                      | Conditions           | Min       | Max | Min       | Max | Note (9)           | Unit |

| t <sub>IN</sub>            | Input pad and buffer delay     |                      |           | 5   |           | 7   | 0                  | ns   |

| t <sub>IO</sub>            | I/O input pad and buffer delay |                      |           | 2   |           | 3   | 0                  | ns   |

| t <sub>LAD</sub>           | Logic array delay              |                      |           | 9   |           | 12  | 25                 | ns   |

| t <sub>OD</sub>            | Output buffer and pad delay    | C1 = 35 pF           |           | 6   |           | 6   | 0                  | ns   |

| t <sub>ZX</sub>            | Output buffer enable delay     |                      |           | 6   |           | 6   | 0                  | ns   |

| t <sub>xz</sub>            | Output buffer disable delay    | C1 = 5 pF, Note (11) |           | 6   |           | 6   | 0                  | ns   |

| t <sub>su</sub>            | Register setup time            |                      | 8         |     | 10        |     | 0                  | ns   |

| t <sub>H</sub>             | Register hold time             |                      | 8         |     | 10        |     | 0                  | ns   |

| t <sub>IC</sub>            | Array clock delay              |                      |           | 9   |           | 12  | 25                 | ns   |

| t <sub>ICS</sub>           | Global clock delay             |                      |           | 4   |           | 5   | 0                  | ns   |

| t <sub>FD</sub>            | Feedback delay                 |                      |           | 3   |           | 3   | -25                | ns   |

| t <sub>CLR</sub>           | Register clear time            |                      |           | 9   |           | 12  | 25                 | ns   |

5

Classic

Altera Corporation

#### Data Sheet

#### AC Operating Conditions: EP1810-35, EP1810-45 Note (5)

| External Timing Parameters |                                    |            | EP1810-35 |     | EP1810-45 |     | Non-Turbo<br>Adder |      |

|----------------------------|------------------------------------|------------|-----------|-----|-----------|-----|--------------------|------|

| Symbol                     | Parameter                          | Conditions | Min       | Max | Min       | Max | Note (9)           | Unit |

| t <sub>PD1</sub>           | Input to non-registered output     | C1 = 35 pF |           | 35  |           | 45  | 30                 | ns   |

| t <sub>PD2</sub>           | I/O input to non-registered output |            |           | 40  |           | 50  | 30                 | ns   |

| t <sub>su</sub>            | Global clock setup time            |            | 25        |     | 30        |     | 30                 | ns   |

| t <sub>H</sub>             | Global clock hold time             |            | 0         |     | 0         |     | 0                  | ns   |

| t <sub>CO1</sub>           | Global clock to output delay       | C1 = 35 pF |           | 20  |           | 25  | 0                  | ns   |

| t <sub>CH</sub>            | Global clock high time             |            | 12        |     | 15        |     | 0                  | ns   |

| t <sub>CL</sub>            | Global clock low time              |            | 12        |     | 15        |     | 0                  | ns   |

| tASU                       | Array clock setup time             |            | 10        |     | 11        |     | 30                 | ns   |

| t <sub>AH</sub>            | Array clock hold time              |            | 15        |     | 18        |     | 0                  | ns   |

| t <sub>ACO1</sub>          | Array clock to output delay        | C1 = 35 pF |           | 35  |           | 45  | 30                 | ns   |

| t <sub>CNT</sub>           | Minimum global clock period        |            |           | 35  |           | 45  | 0                  | ns   |

| f <sub>CNT</sub>           | Maximum internal frequency         | Note (7)   | 28.6      |     | 22.2      |     | 0                  | MHz  |

| f <sub>MAX</sub>           | Maximum clock frequency            | Note (10)  | 40        |     | 33.3      |     | 0                  | MHz  |

| Internal Timing Parameters |                                |                      | EP1810-35 |     | EP1810-45 |     | Non-Turbo<br>Adder |      |  |

|----------------------------|--------------------------------|----------------------|-----------|-----|-----------|-----|--------------------|------|--|

| Symbol                     | Parameter                      | Conditions           | Min       | Max | Min       | Max | Note (9)           | Unit |  |

| t <sub>IN</sub>            | Input pad and buffer delay     |                      |           | 7   |           | 6   | 0                  | ns   |  |

| t <sub>IO</sub>            | I/O input pad and buffer delay |                      |           | 5   |           | 5   | 0                  | ns   |  |

| t <sub>LAD</sub>           | Logic array delay              |                      |           | 19  |           | 28  | 30                 | ns   |  |

| t <sub>OD</sub>            | Output buffer and pad delay    | C1 = 35 pF           |           | 9   |           | 11  | 0                  | ns   |  |

| t <sub>ZX</sub>            | Output buffer enable delay     |                      |           | 9   |           | 11  | 0                  | ns   |  |

| t <sub>XZ</sub>            | Output buffer disable delay    | C1 = 5 pF, Note (11) |           | 9   |           | 11  | 0                  | ns   |  |

| t <sub>su</sub>            | Register setup time            |                      | 10        |     | 10        |     | 0                  | ns   |  |

| t <sub>H</sub>             | Register hold time             |                      | 15        |     | 18        |     | 0                  | ns   |  |

| t <sub>IC</sub>            | Array clock delay              |                      |           | 19  |           | 28  | 30                 | ns   |  |

| t <sub>ICS</sub>           | Global clock delay             |                      |           | 4   |           | 8   | 0                  | ns   |  |

| t <sub>FD</sub>            | Feedback delay                 |                      |           | 6   |           | 7   | -30                | ns   |  |

| t <sub>CLR</sub>           | Register clear time            |                      |           | 24  |           | 32  | 30                 | ns   |  |

#### ALTERA CORP

Data Sheet

| EP1810 EPLD |

|-------------|

#### Notes to tables:

(5)

- The minimum DC input is -0.3 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 7.0 V for periods less than 20 ns under no-load conditions.

- (2) Numbers in parentheses are for military and industrial temperature versions.

- (3) For all Clocks:  $t_R$  and  $t_F = 100$  ns (50 ns for military and industrial temperature versions).

- (4) Typical values are for  $T_A = 25^\circ \text{ C}$  and  $V_{CC} = 5 \text{ V}$ .

- Operating conditions:  $V_{CC} = 5 V \pm 5\%$ ,  $T_A = 0^{\circ} C$  to 70° C for commercial use.

- $V_{CC}$  = 5 V ± 10%,  $T_{A}$  = –40° C to 85° C for industrial use.

- $V_{CC} = 5 V \pm 10\%$ ,  $T_{C} = -55^{\circ} C$  to 125° C for military use.

- (6) When the Turbo Bit is not set (non-turbo mode), an EP910 EPLD enters standby mode if no logic transitions occur for 100 ns (after the last transition).

- (7) Measured with a device programmed as four 12-bit counters.  $I_{CC}$  measured at 0° C.

- (8) Capacitance measured at 25° C. Sample-tested only. Clock-pin capacitance for dedicated Clock inputs only. Pin 21 (high-voltage pin during programming) has a maximum capacitance of 60 pF.

- (9) See "Turbo Bit" earlier in this data sheet.

- (10) Sample-tested only for an output change of 500 mV.

- (11) The  $f_{MAX}$  values represent the highest frequency for pipelined data.

### Product Availability

| Produ            | ct Grade          | Availability                                  |

|------------------|-------------------|-----------------------------------------------|

| Commercial Temp. | (0° C to 70° C)   | EP1810-20, EP1810-25, EP1810-35,<br>EP1810-45 |

| Industrial Temp. | (40° C to 85° C)  | EP1810-25, EP1810-45                          |

| Military Temp.   | (55° C to 125° C) | EP1810-45, Note (1)                           |

Note:

Only military-temperature-range devices are listed. MIL-STD-883-compliant product specifications are provided in "EP1810 MIL-STD-883-Compliant EPLD" in this data sheet and in Military Product Drawings (MPDs). However, only MPDs should be used to prepare Source Control Drawings (SCDs). MPDs are available from Altera Marketing at (408) 894-7000.

Data Sheet

# Pin-Out Information

Table 2 provides pin-out information for EP1810 devices in the PGA package.

| Table      | 2. EP1810 P | GA Pin-l   | Duts     |     |          |            |            |

|------------|-------------|------------|----------|-----|----------|------------|------------|

| Pin        | Function    | Pin        | Function | Pin | Function | Pin        | Function   |

| A2         | 1/0         | <b>B</b> 9 | I/O      | F10 | GND      | K4         | INPUT      |

| A3         | 1/O         | B10        | I/O      | F11 | I/O      | K5         | INPUT      |

| A4         | I/O         | B11        | I/O      | G1  | I/O      | K6         | VCC        |

| A5         | INPUT       | C1         | I/O      | G2  | I/O      | <b>K</b> 7 | INPUT      |

| A6         | CLK4/INPUT  | C2         | I/O      | G10 | I/O      | K8         | INPUT      |

| A7         | CLK3/INPUT  | C10        | I/O      | G11 | I/O      | K9         | I/O        |

| A8         | INPUT       | C11        | I/O      | H1  | 1/O      | K10        | 1/0        |

| A9         | I/O         | D1         | I/O      | H2  | I/O      | K11        | I/O        |

| A10        | I/O         | D2         | I/O      | H10 | I/O      | L2         | I/O        |

| B1         | I/O         | D10        | I/O      | H11 | I/O      | L3         | I/O        |

| B2         | I/O         | D11        | I/O      | J1  | I/O      | L4         | INPUT      |

| B3         | I/O         | E1         | I/O      | J2  | I/O      | L5         | CLK1/INPUT |

| B4         | INPUT       | E2         | I/O      | J10 | I/O      | L6         | CLK2/INPUT |

| B5         | INPUT       | E10        | I/O      | J11 | I/O      | L7         | INPUT      |

| <b>B</b> 6 | vcc         | E11        | I/O      | К1  | I/O      | L8         | I/O        |

| <b>B</b> 7 | INPUT       | F1         | I/O      | К2  | I/O      | L9         | I/O        |

| B8         | INPUT       | F2         | GND      | кз  | I/O      | L10        | I/O        |

٠