# QUAD PROGRAMMABLE PCM CODEC WITH MPI INTERFACE

IDT821054

#### **FEATURES**

- · 4-channel CODEC with on-chip digital filters

- Software selectable A/µ-law, linear code conversion

- Meets ITU-T G.711 G.714 requirements

- · Programmable digital filters adapting to system demands:

- AC impedance matching

- Transhybrid balance

- Frequency response correction

- Gain setting

- · Supports two programmable PCM buses

- Flexible PCM interface with up to 128 programmable time slots, data rate from 512 kbits/s to 8.192 Mbits/s

- · MPI control interface

- · Broadcast mode for coefficient setting

- 7 SLIC signaling pins (including 2 debounced pins) per channel

- · Fast hardware ring trip mechanism

- 2 programmable tone generators per channel for testing, ringing and DTMF generation

- 1 programmable FSK generator for sending Caller-ID messages

- Two programmable chopper clocks

- Master clock frequency selectable: 1.536 MHz, 1.544 MHz, 2.048 MHz, 3.072 MHz, 3.088 MHz, 4.096 MHz, 6.144 MHz, 6.176 MHz or 8.192 MHz

- Advanced test capabilities:

- 3 analog loopback tests

- 5 digital loopback tests

- Level metering function

- High analog driving capability (300  $\Omega$  AC)

- TTL/CMOS compatible digital I/O

- · CODEC identification

- +5 V single power supply

- Low power consumption

- Operating temperature range: -40°C to +85°C

- Package available: 64 Pin PQFP

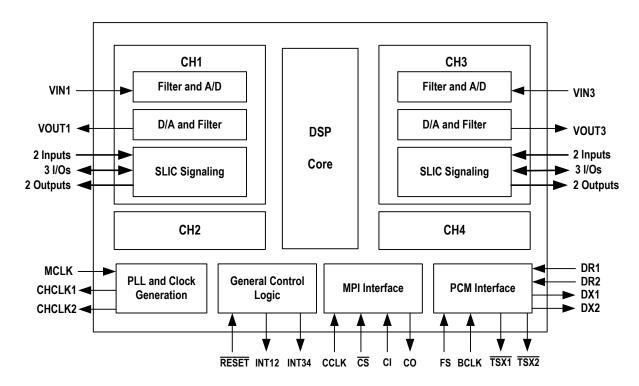

#### **FUNCTIONAL BLOCK DIAGRAM**

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

INDUSTRIAL TEMPERATURE RANGE

**FEBRUARY 26, 2003**

#### **DESCRIPTION**

The IDT821054 is a feature rich, single-chip, programmable 4-channel PCM CODEC with on-chip filters. Besides the  $\mu\text{-Law/A-Law}$  companding and linear coding/decoding (14 effective bits + 2 extra sign bits), the IDT821054 also provides 1 FSK generator for sending Caller-ID messages, 2 programmable tone generators per channel (which can generate ring signals) and 2 programmable chopper clocks for SLICs.

The digital filters in the IDT821054 provide necessary transmit and receive filtering for voice telephone circuits to interface with time-division multiplexed systems. An integrated programmable DSP realizes AC impedance matching, transhybrid balance, frequency response correction and gain adjustment functions. The IDT821054 supports 2 PCM buses with programmable sampling edge, which allows an extra delay of up to 7 clocks. Once the delay is determined, it is effective to all

four channels of the IDT821054. The device also provides 7 signaling pins per channel for SLICs.

The IDT821054 is programmed via a Microprocessor Interface (MPI). Two PCM buses are provided to transfer the compressed or linear PCM data

The device offers strong test capability with several analog/digital loopbacks and level metering function. It brings convenience to system maintenance and diagnosis.

A unique feature of "Hardware Ring Trip" is implemented in the IDT821054. When an off-hook signal is detected, the IDT821054 will reverse an output pin to stop the ringing signal immediately.

The IDT821054 can be used in digital telecommunication applications such as Central Office Switch, PBX, DLC and Integrated Access Devices (IADs), i.e. VoIP and VoDSL.

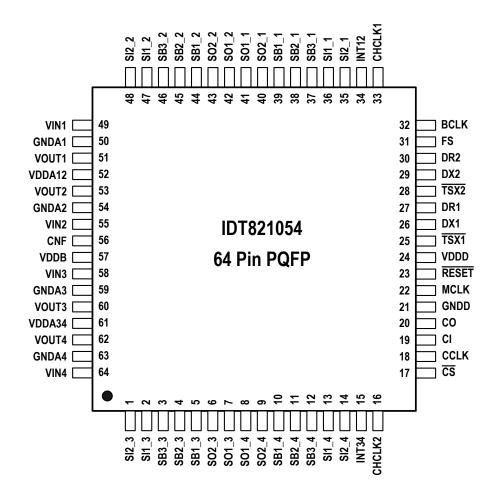

#### PIN CONFIGURATION

# **TABLE OF CONTENTS**

| 1 | Pin D | Description                                        | 7  |

|---|-------|----------------------------------------------------|----|

| 2 | Func  | ctional Description                                |    |

|   | 2.1   | MPI/PCM Interface                                  |    |

|   |       | 2.1.1 Microprocessor Interface (MPI)               |    |

|   |       | 2.1.2 PCM Bus                                      |    |

|   | 2.2   | DSP Programming                                    | 11 |

|   |       | 2.2.1 Signal Processing                            | 11 |

|   |       | 2.2.2 Gain Adjustment                              | 11 |

|   |       | 2.2.3 Impedance Matching                           | 11 |

|   |       | 2.2.4 Transhybrid Balance                          |    |

|   |       | 2.2.5 Frequency Response Correction                |    |

|   | 2.3   | SLIC Control                                       | 12 |

|   |       | 2.3.1 SI1 and SI2                                  | 12 |

|   |       | 2.3.2 SB1, SB2 and SB3                             |    |

|   |       | 2.3.3 SO1 and SO2                                  |    |

|   | 2.4   | Hardware Ring Trip                                 |    |

|   | 2.5   | Interrupt and Interrupt Enable                     |    |

|   | 2.6   | Debounce Filters                                   |    |

|   | 2.7   | Chopper Clock                                      |    |

|   | 2.8   | Dual Tone and Ring Generation                      |    |

|   | 2.9   | FSK SIGNAL GENERATION                              |    |

|   | 2.10  |                                                    |    |

|   | 2.11  |                                                    |    |

|   | 2.12  | Power Down/Suspend Mode                            | 16 |

| 3 | Oper  | rating The IDT821054                               | 17 |

|   | 3.1   | Programming Description                            |    |

|   |       | 3.1.1 Command Type and Format                      |    |

|   |       | 3.1.2 Addressing the Local Registers               | 17 |

|   |       | 3.1.3 Addressing the Global Registers              |    |

|   |       | 3.1.4 Addressing the Coe-RAM                       | 17 |

|   |       | 3.1.5 ADDRESSING FSK-RAM                           | 18 |

|   |       | 3.1.6 Programming Examples                         | 18 |

|   |       | 3.1.6.1 Example of Programming Local Registers     | 18 |

|   |       | 3.1.6.2 Example of Programming Global Registers    | 18 |

|   |       | 3.1.6.3 Example of Programming the Coefficient-RAM |    |

|   |       | 3.1.6.4 Example of Programming the FSK-RAM         | 19 |

|   | 3.2   | Power-on Sequence                                  |    |

|   | 3.3   | Default State After Reset                          |    |

|   | 3.4   | Registers Description                              |    |

|   |       | 3.4.1 Registers Overview                           |    |

|   |       | 3.4.2 Global Registers List                        |    |

|   |       | 3.4.3 Local Registers List                         | 31 |

| 4 | Abso  | olute Maximum Ratings                              | 35 |

| 5 | Reco  | ommended DC Operating Conditions                   | 35 |

| 6 | Flect | trical Characteristics                             | 31 |

| 0 | 6.1   | Digital Interface                                  |    |

|   | 6.2   | Power Dissipation                                  |    |

|   | 6.3   | Analog Interface                                   |    |

|   |       |                                                    |    |

| 7 | Trans | smission Characteristics                           |    |

|   | 7.1   | Absolute Gain                                      |    |

|   | 7.2   | Gain Tracking                                      |    |

|   | 7.3   | Frequency Response                                 | 37 |

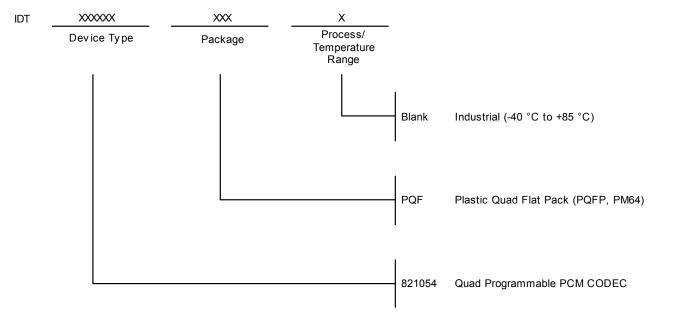

| 10 | Orde  | ering Information                | 44 |

|----|-------|----------------------------------|----|

| 9  | Appe  | endix: ID1821034 Goe-KAM Mapping | 43 |

| ^  | A     | endix: IDT821054 Coe-RAM Mapping | 42 |

|    | 8.3   | PCM Interface Timing             | 42 |

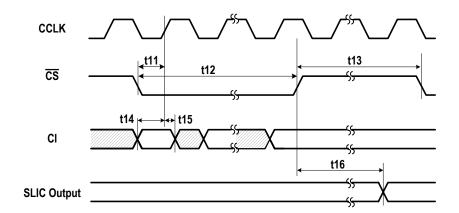

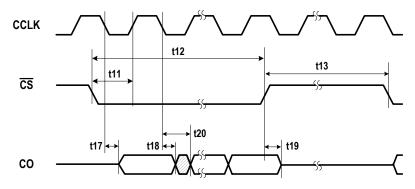

|    | 8.2   | Microprocessor Interface Timing  | 41 |

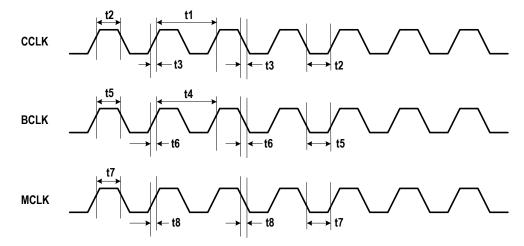

|    | 8.1   | Clock Timing                     | 40 |

| 8  | Timir | ng Characteristics               | 40 |

|    | 7.8   | Intrachannel Crosstalk           | 39 |

|    | 7.7   | Interchannel Crosstalk           | 39 |

|    | 7.6   | Noise                            | 39 |

|    | 7.5   | Group Delay  Distortion          | 38 |

|    | 7.4   | Group Delay                      | 38 |

# **LIST OF FIGURES**

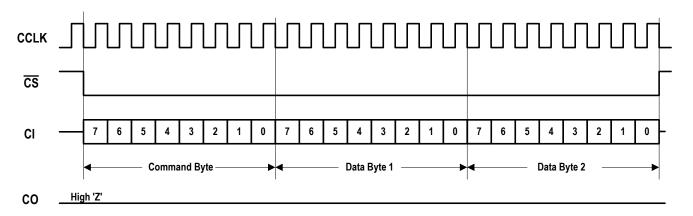

| Figure - 1  | An Example of the MPI Interface Write Operation           | 9  |

|-------------|-----------------------------------------------------------|----|

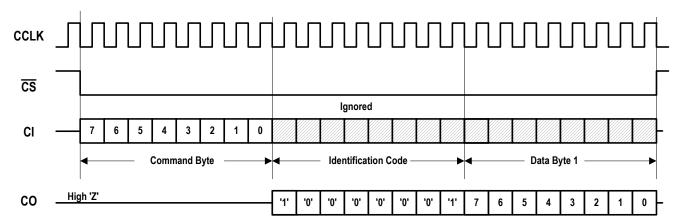

| Figure - 2  | An Example of the MPI Interface Read Operation (ID = 81H) | 🤅  |

| Figure - 3  | Sampling Edge Selection Waveform                          | 10 |

| Figure - 4  | Signal Flow for Each Channel                              | 11 |

| Figure - 5  | Debounce Filter                                           | 13 |

| Figure - 6  | General Procedure of Sending Caller-ID Signal             | 14 |

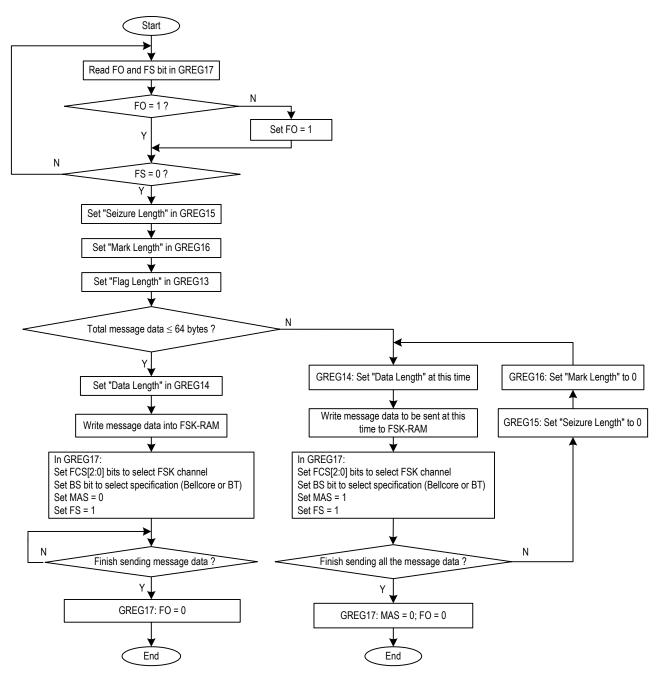

| Figure - 7  | A Recommended Procedure of Programming the FSK Generator  | 15 |

| Figure - 8  | Clock Timing                                              |    |

| Figure - 9  | MPI Input Timing                                          |    |

| Figure - 10 | MPI Output Timing                                         | 41 |

| Figure - 11 | Transmit and Receive Timing                               | 42 |

| Figure - 12 | Typical Frame Sync Timing (2 MHz Operation)               |    |

| Figure - 13 | Coe-RAM Mapping                                           |    |

|             |                                                           |    |

# **LIST OF TABLES**

| Table - 1 | BT/Bellcore Standard of FSK Signal | 14 |

|-----------|------------------------------------|----|

| Table - 2 | Consecutive Adjacent Addressing    | 17 |

| Table - 3 | Global Registers (GREG) Mapping    | 22 |

| Table - 4 | Local Registers (LREG) Mapping     | 23 |

| Table - 5 | Coe-RAM Address Allocation         | 43 |

# 1 PIN DESCRIPTION

| Name                                | Туре   | Pin Number                                      | Description                                                                                                                                                                      |

|-------------------------------------|--------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GNDA1<br>GNDA2<br>GNDA3<br>GNDA4    | Ground | 50<br>54<br>59<br>63                            | Analog Ground. All ground pins should be connected together.                                                                                                                     |

| GNDD                                | Ground | 21                                              | Digital Ground. All digital signals are referred to this pin.                                                                                                                    |

| VDDA12<br>VDDA34                    | Power  | 52<br>61                                        | <b>+5 V Analog Power Supply.</b> These pins should be connected to ground via a 0.1 μF capacitor. All power supply pins should be connected together.                            |

| VDDD                                | Power  | 24                                              | +5 V Digital Power Supply.                                                                                                                                                       |

| VDDB                                | Power  | 57                                              | +5 V Analog Power Supply.  This pin should be connected to ground via a 0.1 μF capacitor. All power supply pins should be connected together.                                    |

| CNF                                 | _      | 56                                              | Capacitor Noise Filter.  This pin should be connected to ground via a 0.22 μF capacitor.                                                                                         |

| VIN1-4                              | I      | 49, 55, 58, 64                                  | Analog Voice Inputs of Channel 1-4. These pins should be connected to the corresponding SLIC via a 0.22 µF capacitor.                                                            |

| VOUT1-4                             | 0      | 51, 53, 60, 62                                  | Voice Frequency Receiver Outputs of Channel 1-4. These pins can drive 300 $\Omega$ AC load. It can drive transformers directly.                                                  |

| SI1_(1-4)<br>SI2_(1-4)              | I      | 36, 47, 2, 13<br>35, 48, 1, 14                  | SLIC Signalling Inputs with debounce function for Channel 1-4.                                                                                                                   |

| SB1_(1-4)<br>SB2_(1-4)<br>SB3_(1-4) | I/O    | 39, 44, 5, 10<br>38, 45, 4, 11<br>37, 46, 3, 12 | Bi-directional SLIC Signalling I/Os for Channel 1-4. These pins can be individually programmed as input or output.                                                               |

| SO1_(1-4)<br>SO2_(1-4)              | 0      | 41, 42, 7, 8<br>40, 43, 6, 9                    | SLIC Signalling Outputs for Channel 1-4.                                                                                                                                         |

| DX1                                 | 0      | 26                                              | Transmit PCM Data Output, PCM Highway One. Transmit PCM Data to PCM highway one. This pin is a tri-state output pin.                                                             |

| DX2                                 | 0      | 29                                              | Transmit PCM Data Output, PCM Highway Two. Transmit PCM Data to PCM highway two. This pin is a tri-state output pin.                                                             |

| DR1                                 | I      | 27                                              | Receive PCM Data Input, PCM Highway One. The PCM data is received from PCM highway one (DR1) or two (DR2). The receive PCM highway is selected by local register LREG6.          |

| DR2                                 | I      | 30                                              | Receive PCM Data Input, PCM Highway Two. The PCM data is received from PCM highway one (DR1) or two (DR2). The receive PCM highway is selected by local register LREG6.          |

| FS                                  | I      | 31                                              | Frame Synchronization. FS is an 8 kHz synchronization clock that identifies the beginning of the PCM frame.                                                                      |

| BCLK                                | I      | 32                                              | Bit Clock. This pin clocks out the PCM data to DX1 or DX2 pin and clocks in PCM data from DR1 or DR2 pin. It may vary from 512 kHz to 8.192 MHz and should be synchronous to FS. |

| TSX1<br>TSX2                        | 0      | 25<br>28                                        | Transmit Output Indicator. The TSX1 pin becomes low when PCM data is transmitted via DX1. Open-drain. The TSX2 pin becomes low when PCM data is transmitted via DX2. Open-drain. |

| Name      | Туре | Pin Number | Description                                                                                                                                                                                                         |

|-----------|------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>cs</u> | I    | 17         | Chip Selection. A logic low level on this pin enables the Serial Control Interface.                                                                                                                                 |

| CI        | I    | 19         | Serial Control Interface Data Input. Control data input pin. CCLK determines the data rate.                                                                                                                         |

| СО        | 0    | 20         | Serial Control Interface Data Output (Tri-State). Control data output pin. CCLK determines the data rate.                                                                                                           |

|           |      | 18         | Serial Control Interface Clock. This is the clock for the Serial Control Interface. It can be up to 8.192 MHz.                                                                                                      |

| MCLK      | I    | 22         | Master Clock Input. This pin provides the clock for the DSP of the IDT821054. The frequency of the MCLK can be 1.536 MHz, 1.544 MHz, 2.048 MHz, 3.072 MHz, 3.088 MHz, 4.096 MHz, 6.144 MHz, 6.176 MHz or 8.192 MHz. |

| RESET     | I    | 23         | Reset Input. Forces the device to default mode. Active low.                                                                                                                                                         |

| INT12     | 0    | 34         | Interrupt Output Pin for Channel 1-2. Active high interrupt signal for Channel 1 and 2, open-drain. It reflects the changes on the corresponding SLIC input pins.                                                   |

| INT34     | 0    | 15         | Interrupt Output Pin for Channel 3-4. Active high interrupt signal for Channel 3 and 4, open-drain. It reflects the changes on the corresponding SLIC input pins.                                                   |

| CHCLK1    | 0    | 33         | Chopper Clock Output One. Provides a programmable output signal (2 -28 ms) synchronous to MCLK.                                                                                                                     |

| CHCLK2    | 0    | 16         | Chopper Clock Output Two. Provides a programmable output signal (256 kHz, 512 kHz or 16.384 MHz) synchronous to MCLK.                                                                                               |

#### 2 FUNCTIONAL DESCRIPTION

The IDT821054 is a four-channel PCM CODEC with on-chip digital filters. It provides a four-wire solution for the subscriber line circuitry in digital switches. The IDT821054 converts analog voice signals to digital PCM samples and digital PCM samples back to analog voice signals. The digital filters are used to bandlimit the voice signals during conversion. High performance oversampling Analog-to-Digital Converters (ADC) and Digital-to-Analog Converters (DAC) in the IDT821054 provide the required conversion accuracy. The associated decimation and interpolation filtering is performed by both dedicated hardware and Digital Signal Processor (DSP). The DSP also handles all other necessary procession such as PCM bandpass filtering, sample rate conversion and PCM companding.

#### 2.1 MPI/PCM INTERFACE

A serial Microprocessor Interface (MPI) is provided for the master device to control the IDT821054. Two PCM buses are provided to transfer the digital voice data.

#### 2.1.1 MICROPROCESSOR INTERFACE (MPI)

The internal configuration registers (local/global), the SLIC signaling

interface and the Coefficient-RAM of the IDT821054 are programmed by the master device via MPI, which consists of four lines (pins): CCLK,  $\overline{CS}$ , CI and CO. All commands and data are aligned in byte (8 bits) and transferred via the MPI interface. CCLK is the clock of the MPI interface. The frequency of CCLK can be up to 8.192 MHz.  $\overline{CS}$  is the chip selection pin. A low level on  $\overline{CS}$  enables the MPI interface. CI and CO are data input and data output pins, carrying control commands and data bytes to/from the IDT821054.

The data transfer is synchronized to the CCLK signal. The contents of CI is latched on the rising edges of CCLK, while CO changes on the falling edges of CCLK. The CCLK signal is the only reference of CI and CO pins. Its duty and frequency may not necessarily be standard.

When the  $\overline{\text{CS}}$  pin becomes low, the IDT821054 treats the first byte on the CI pin as command and the rest as data. To write another command, the  $\overline{\text{CS}}$  pin must be changed from low to high to finish the previous command and then changed from high to low to indicate the start of a new command. When a read/write operation is completed, the  $\overline{\text{CS}}$  pin must be set to high in 8-bit time.

During the execution of commands that are followed by output data byte(s), the IDT821054 will not accept any new commands from the CI pin. But the data transfer sequence can be interrupted by setting the  $\overline{\text{CS}}$  pin to high at any time. See Figure - 1 and Figure - 2 for examples of MPI write and read operation timing diagrams.

Figure - 1 An Example of the MPI Interface Write Operation

Figure - 2 An Example of the MPI Interface Read Operation (ID = 81H)

#### 2.1.2 PCM BUS

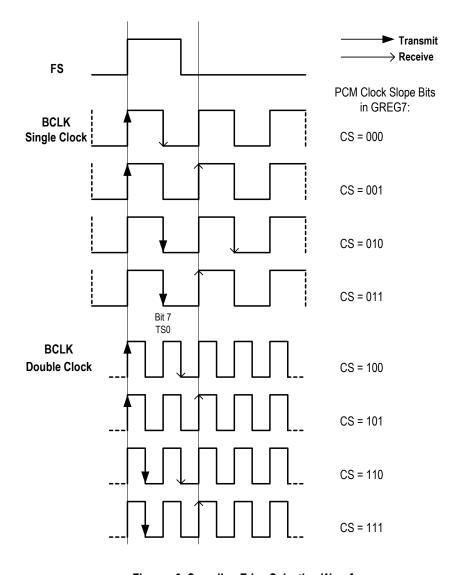

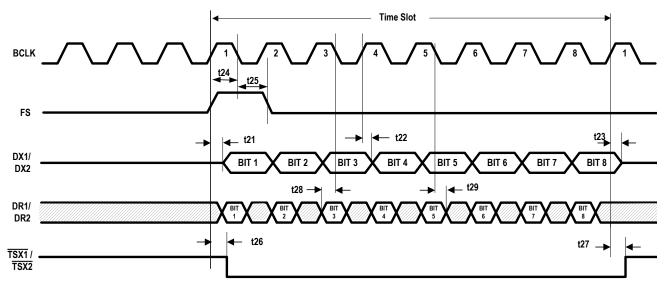

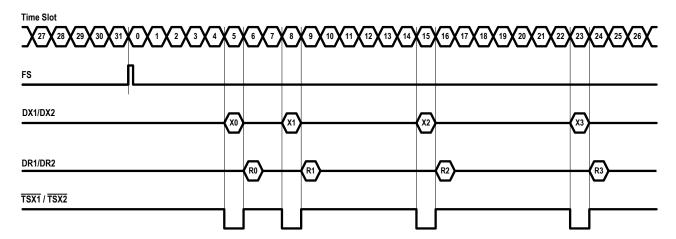

The IDT821054 provides two flexible PCM buses for all 4 channels. The digital PCM data can be compressed (A/ $\mu$ -law) or linear code. As shown in Figure - 3, the data rate can be configured as same as the Bit Clock (BCLK) or half of it. The PCM data is transmitted or received either on the rising edges or on the falling edges of the BCLK signal. The transmit and receive time slots can offset from the FS signal by 0 to 7 periods of BCLK. All these configurations are made by global register GREG7, which is effective for all four channels.

The PCM data of each channel can be assigned to any time slot of the PCM bus. The number of available time slots is determined by the frequency of the BCLK signal. For example, if the frequency is 512 kHz, 8 time slots (TS0 to TS7) are available. If the frequency is 1.024 MHz, 16 time slots (TS0 to TS15) are available. The IDT821054 accepts BCLK frequency of 512 kHz to 8.192 MHz at increments of 64 kHz.

When compressed PCM code (8-bit wide) is selected, the voice data of one channel occupies one time slot. The TT[6:0] bits in local register LREG5 select the transmit time slot for each channel, while the RT[6:0] bits in LREG6 select the receive time slot for each channel.

When linear PCM code is selected, the voice data is a 16-bit 2's

complement number (b13 to b0 are effective bits, b15 and b14 are as same as the sign bit b13). So, the voice data of one channel occupies one time slot group, which consists of 2 adjacent time slots. The TT[6:0] bits in LREG5 select a transmit time slot group for the specified channel. If TT[6:0] = n(d), it means that time slots TS(2n+1) and TS(2n+2) are selected. For example, if TT[6:0] = 00H, it means that TS0 and TS1 are selected. The RT[6:0] bits in LREG6 select a receive time slot group for the specified channel in the same way.

The PCM data of each individual channel can be clocked out to transmit PCM highway one (DX1) or two (DX2) on the programmed edges of BCLK according to time slot assignment. The transmit PCM highway is selected by the THS bit in LREG5. The frame sync (FS) pulse identifies the beginning of a transmit frame (TS0). The PCM data is serially transmitted on DX1 or DX2 with MSB first.

The PCM data of each individual channel is received from receive PCM highway one (DR1) or two (DR2) on the programmed edges of BCLK according to time slot assignment. The receive PCM highway is selected by the RHS bit in LREG6. The frame sync (FS) pulse identifies the beginning of a receive frame (TS0). The PCM data is serially received from DR1 or DR2 with MSB first.

Figure - 3 Sampling Edge Selection Waveform

#### 2.2 DSP PROGRAMMING

#### 2.2.1 SIGNAL PROCESSING

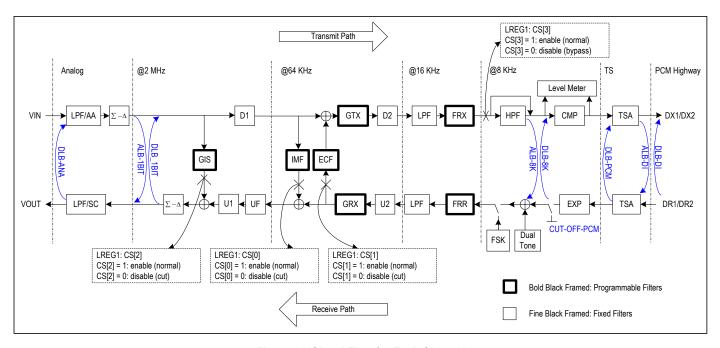

Several blocks are programmable for signal processing. This allows users to optimize the performance of the IDT821054 for the system. Figure - 4 shows the signal flow for each channel and indicates the programmable blocks.

The programmable digital filters are used to adjust gain and

impedance, balance transhybrid and correct frequency response. All the coefficients of the digital filters can be calculated automatically by a software provided by IDT. When users provide accurate SLIC model, impedance and gain requirements, this software will calculate all the coefficients automatically. After loading these coefficients to the coefficient RAM of the IDT821054, the final AC characteristics of the line card (consists of SLIC and CODEC) will meet the ITU-T specifications.

Figure - 4 Signal Flow for Each Channel

#### **Abbreviation List:**

LPF/AA: Anti-Alias Low-pass Filter LPF/SC: Smoothing Low-pass Filter

LPF: Low-pass Filter HPF: High-pass Filter

GIS: Gain for Impedance Scaling D1: 1st Down Sample Stage D2: 2nd Down Sample Stage U1: 1st Up Sample Stage U2: 2nd Up Sample Stage

UF: Up Sampling Filter (64 k - 128 k)

IMF: Impedance Matching Filter ECF: Echo Cancellation Filter GTX: Gain for Transmit Path GRX: Gain for Receive Path

FRX: Frequency Response Correction for Transmit FRR: Frequency Response Correction for Receive

CMP: Compression EXP: Expansion

TSA: Time Slot Assignment

#### 2.2.2 GAIN ADJUSTMENT

The analog gain and digital gain of each channel can be adjusted separately in the IDT821054.

For each individual channel, the analog A/D gain in the transmit path can be selected as 0 dB or 6 dB. The selection is done by the GAD bit in LREG9. It is 0 dB by default.

For each individual channel, the analog D/A gain in the receive path can be selected as 0 dB or -6 dB. The selection is done by the GDA bit in LREG9. It is 0 dB by default.

For each individual channel, the digital gain in the transmit path (GTX) is programmable from -3 dB to +12 dB with minimum 0.1 dB step. If the CS[5] bit in local register LREG1 is '0', the GTX filter is disabled. If the CS[5] bit is '1', the GTX is programmed by the coefficient RAM.

For each individual channel, the digital gain in the receive path

(GRX) is programmable from -12 dB to +3 dB with minimum 0.1 dB step. If the CS[7] bit in LREG1 is '0', the GRX filter is disabled. If the CS[7] bit is '1', the GRX is programmed by the coefficient RAM.

#### 2.2.3 IMPEDANCE MATCHING

The IDT821054 provides a programmable feedback path from VIN to VOUT for each channel. This feedback synthesizes the two-wire impedance of the SLIC. The programmable Impedance Matching Filter (IMF) and Gain of Impedance Scaling filter (GIS) work together to realize impedance matching. If the CS[0] bit in LREG1 is '0', the IMF is disabled. If the CS[0] bit is '1', the IMF coefficient is programmed by the coefficient RAM. If the CS[2] bit in LREG1 is '0', the GIS filter is disabled. If the CS[2] bit is '1', the GIS coefficient is programmed by the coefficient RAM.

#### 2.2.4 TRANSHYBRID BALANCE

The ECF filter is used to adjust transhybrid balance and ensure that the echo cancellation meets the ITU-T specifications. If the CS[1] bit in LREG1 is '0', the ECF filter is disabled. If the CS[1] bit is '1', the ECF coefficient is programmed by the coefficient RAM.

#### 2.2.5 FREQUENCY RESPONSE CORRECTION

The IDT821054 provides two filters that can be programmed to correct any frequency distortion caused by the impedance matching filter. They are the Frequency Response Correction in the Transmit path filter (FRX) and the Frequency Response Correction in the Receive path filter (FRR). If the CS[4] bit in LREG1 is '0', the FRX filter is disabled. If the CS[4] bit is '1', the FRX coefficient is programmed by the coefficient RAM. If the CS[6] bit in LREG1 is '0', the FRR filter is disabled. If the CS[6] bit is '1', the FRR coefficient is programmed by the coefficient RAM.

Refer to "9 Appendix: IDT821054 Coe-RAM Mapping" for the address of the GTX, GRX, FRX, FRR, GIS, ECF and IMF coefficients.

#### 2.3 SLIC CONTROL

The SLIC control interface of the IDT821054 consists of 7 pins per channel: 2 inputs SI1 and SI2, 3 I/Os SB1 to SB3, and 2 outputs SO1 and SO2.

#### 2.3.1 SI1 AND SI2

The SLIC inputs SI1 and SI2 can be read in 2 ways - globally for all 4 channels or locally for each individual channel.

The SI1 and SI2 status of all 4 channels can be read via global register GREG9. The SIA[3:0] bits in this register represent the debounced SI1 data of Channel 4 to Channel 1. The SIB[3:0] bits in this register represent the debounced SI2 data of Channel 4 to Channel 1.

Both the SI1 and SI2 pins can be connected to off-hook, ring trip, ground key signals or other signals. The global register GREG9 provides a more efficient way to obtain time-critical data such as on/off-hook and ring trip information from the SLIC input pins SI1 and SI2.

The SI1 and SI2 status of each channel can also be read via the corresponding local register LREG4.

#### 2.3.2 SB1, SB2 AND SB3

The SLIC I/O pin SB1 of each channel can be configured as input or output via global register GREG10. The SB1C[3:0] bits in GREG10 determine the SB1 directions of Channel 4 to Channel 1: '0' means input and '1' means output. The SB2C[3:0] bits in GREG11 and the SB3C[3:0] bits in GREG12 respectively determine the SB2 and SB3 directions of Channel 4 to Channel 1 in the same way.

If the SB1, SB2 or SB3 pin is selected as input, its information can be read from both global and local registers. The SB1[3:0], SB2[3:0] and SB3[3:0] bits in global registers GREG10, GREG11 and GREG12 respectively contain the information of SB1, SB2 and SB3 for all four channels. Users can also read the information of SB1, SB2 and SB3 of the specified channel from local register LREG4.

If the SB1, SB2 and SB3 pins are configured as outputs, data can only be written to them via GREG10, GREG11 and GREG12 respectively.

#### 2.3.3 SO1 AND SO2

The control data can only be written to the two output pins SO1 and SO2 by local register LREG4 on a per-channel basis. When being read, the SO1 and SO2 bits in LREG4 will be read out with the data written to them in the previous write operation.

#### 2.4 HARDWARE RING TRIP

In order to avoid the damage caused by high voltage ring signal, the IDT821054 provides a hardware ring trip function to respond to the off-hook signal as fast as possible. This function is enabled by setting the RTE bit in GREG8 to '1'.

The off-hook signal can be input via either SI1 or SI2 pin, while the ring control signal can be output via any of the SO1, SO2, SB1, SB2 and SB3 pins (assume that SB1-SB3 are configured as outputs). The IS bit in GREG8 is used to select an input pin and the OS[2:0] bits are used to select an output pin.

When a valid off-hook signal arrives at the selected input pin (SI1 or SI2), the IDT821054 will turn off the ring signal by inverting the logic level of the selected output pin (SO1, SO2, SB1, SB2 or SB3), regardless of the value of the corresponding SLIC output control register (the value should be changed later). This function provides a much faster response to off-hook signals than the software ring trip which turns off the ring signal by changing the value of the corresponding register.

The IPI bit in GREG8 is used to indicate the valid polarity of the input pin. If the off-hook signal is active low, the IPI bit should be set to '0'. If the off-hook signal is active high, the IPI bit should be set to '1'. The OPI bit in GREG8 is used to indicate the valid polarity of the output pin. If the ring control signal is required to be low in normal status and high to activate a ring, the OPI bit should be set to '1'. If it is required to be high in normal status and low to activate a ring, the OPI bit should be set to '0'.

Here is an example: In a system where the off-hook signal is active low and ring control signal is active high, the IPI bit should be set to '0' and the OPI bit should be set to '1'. In normal status, the selected input (off-hook signal) is high and the selected output (ring control signal) is low. When the ring is activated by setting the output (ring control signal) to high, a low pulse appearing on the input (off-hook signal) will inform the device to invert the output to low and cut off the ring signal.

#### 2.5 INTERRUPT AND INTERRUPT ENABLE

An interrupt mechanism is provided in the IDT821054 for reading the SLIC input state. Each change of the SLIC input state will generate an interrupt

Any of the SLIC inputs including SI1, SI2, SB1, SB2 and SB3 (if SB1-SB3 are configured as inputs) can be an interrupt source. As SI1 and SI2 signals are debounced while the SB1 to SB3 signals are not, users should pay more attention to the interrupt sources of SB1 to SB3.

Local register LREG2 is used to enable/disable the interrupts. Each bit of IE[4:0] in LREG2 corresponds to one interrupt source of the specified channel. When one bit of IE[4:0] is '0', the corresponding interrupt is ignored (disabled), otherwise, the corresponding interrupt is recognized (enabled).

Multiple interrupt sources can be enabled at the same time. All interrupts can be cleared simultaneously by executing a write operation to global register GREG2. Additionally, the interrupts caused by all four

channels' SI1 and SI2 status changes can be cleared by applying a read operation to GREG9. If SB1, SB2 and SB3 pins are configured as inputs, a read operation to GREG10, GREG11 and GREG12 clears the interrupt generated by the corresponding SB port of all four channels. A read operation to LREG4 clears all 7 interrupt sources of the specified channel.

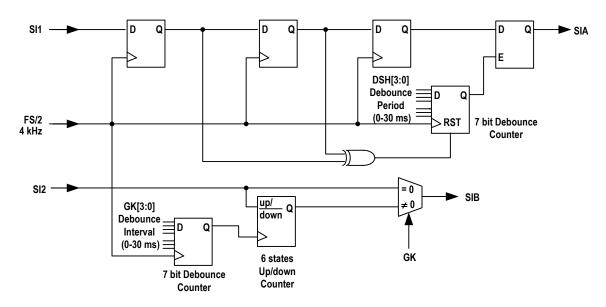

#### 2.6 DEBOUNCE FILTERS

For each channel, the IDT821054 provides two debounce filter circuits: Debounced Switch Hook (DSH) Filter for the SI1 signal and Ground Key (GK) Filter for the SI2 signal. See Figure - 5 for details. The two debounce filters are used to buffer the input signals on SI1 and SI2 pins before changing the state of the SLIC Debounced Input SI1/SI2 Register (GREG9). The Frame Sync (FS) signal is necessary for both DSH and GK filters.

The DSH[3:0] bits in LREG3 are used to program the debounce period of the SI1 input of the corresponding channel. The DSH filter is initially clocked at half of the frame sync rate (250  $\mu$ s). Any data changing at this sample rate resets a counter that clocks at the rate of 2 ms. The value of the counter is programmable from 0 to 30 via LREG3.

The debounced SI1 signals of Channel 4 to 1 are written to the SIA[3:0] bits in GREG9. The corresponding SIA bit will not be updated until the value of the counter is reached. The SI1 pin usually contains the SLIC switch hook status.

The GK[3:0] bits in LREG3 are used to program the debounce interval of the SI2 input of the corresponding channel. The debounced SI2 signals of Channel 4 to 1 are written to the SIB[3:0] bits in GREG9. The GK debounce filter consists of a six-state up/down counter that ranges between 0 and 6. This counter is clocked by the GK timer at the sampling period of 0-30 ms, which is programmed via LREG3. If the sampled value is low, the value of the counter will be decremented by each clock pulse. If the sampled value is high, the value of the counter is incremented by each clock pulse. When the value increases to 6, it sets a latch whose output is routed to the corresponding SIB bit. If the value decreases to 0, the latch will be cleared and the output bit will be set to 0. In other cases, the latch and the SIB status remain in their previous state without being changed. In this way, at least six consecutive GK clocks with the debounce input remaining at the same state can effect an output change.

Figure - 5 Debounce Filter

#### 2.7 CHOPPER CLOCK

The IDT821054 provides two programmable chopper clock outputs CHCLK1 and CHCLK2. They can be used to drive the power supply switching regulators on SLICs. The two chopper clocks are synchronous to MCLK. The CHCLK1 outputs a signal which clock cycle is programmable from 2 to 28 ms. The CHCLK2 outputs a signal which frequency can be 256 kHz, 512 kHz or 16.384 MHz. The frequencies of the two chopper clocks are programmed by global register GREG5.

#### 2.8 DUAL TONE AND RING GENERATION

The IDT821054 provides two tone generators (tone generator 0 and tone generator 1) for each channel. They can produce signals such as test tone, DTMF, dial tone, busy tone, congestion tone and Caller-ID Alerting Tone, and output it to the VOUT pin.

The dual tone generators of each channel can be enabled by setting the TEN0 and TEN1 bits in LREG10 to '1'respectively.

The frequency and amplitude of the tone signal are programmed by the Coe-RAM. The frequency and amplitude coefficients are calculated by the following formulas:

Frequency coefficient =  $32767*\cos(f/8000*2*\pi)$

Amplitude coefficient = A \* 32767 \*  $sin(f / 8000 * 2 * \pi)$

Herein, 'f' is the desired frequency of the tone signal, 'A' is the scaling parameter of the amplitude. The range of 'A' is from 0 to 1.

A = 1, corresponds to the maximum amplitude of 1.57 V.

A = 0, corresponds to the minimum amplitude of 0 V.

It is a linear relationship between 'A' and the amplitude. That is, if A= $\beta$  ( 0< $\beta$ <1), the amplitude will be 1.57 \*  $\beta$  (V).

The frequency range is from 25 Hz to 3400 Hz. The frequency tolerances are as the following:

25 Hz < f < 40 Hz, tolerance <  $\pm$ 12%

40 Hz < f < 60 Hz, tolerance <  $\pm 5\%$ 60 Hz < f < 100 Hz, tolerance <  $\pm 2.5\%$ 100 Hz < f < 3400 Hz, tolerance <  $\pm 1\%$

The frequency and amplitude coefficients should be converted to corresponding hexadecimal values before being written to the Coe-RAM. Refer to "9 Appendix: IDT821054 Coe-RAM Mapping" for the address of the tone coefficients.

The ring signal is a special signal generated by the dual tone generators. When only one tone generator is enabled, or dual tone generators produce the same tone signal and frequency of the tone meets the ring signal requirement (10 Hz to 100 Hz), a ring signal will be generated and output to the VOUT pin.

#### 2.9 FSK SIGNAL GENERATION

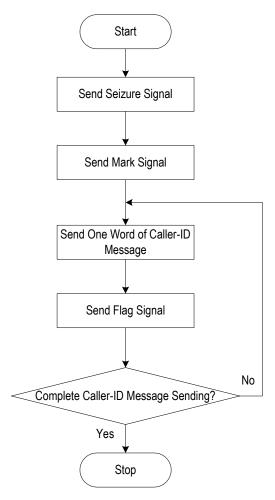

The IDT821054 has a built-in FSK generator for all four channels to send Caller-ID signals. The general procedure of sending a Caller-ID signal is as shown in Figure - 6.

Figure - 6 General Procedure of Sending Caller-ID Signal

The Seizure Signal is a series of '01' pairs. Seizure Length, i.e. the number of the '01' pairs of the Seizure Signal, is programmable. It is two times of the value of the SL[7:0] bits in GREG15. For example, if SL[7:0]

= 5 (d), the Seizure Length will be 10 (d).

The Mark Signal is a series of '1'. The length of the Mark Signal (Mark Length) is determined by the ML[7:0] bits in GREG16.

The Caller-ID message should be written to the FSK-RAM before it is sent out. The FSK-RAM consists of 32 words, and each word consists of two bytes, so it can contain up to 64 bytes of message at one time. If the total message is longer than 64 bytes, it should be written to the FSK-RAM at two or more times. Data Length, i.e. the number of the data bytes that are written to the FSK-RAM for transmission, is set by the DL[7:0] bits in GREG14.

One 'Word' of the Caller-ID message consists of 10 bits: one Start Bit at the beginning, one Stop Bit at the end and eight bits of Caller-ID message in the middle. For the IDT821054, the eight bits of Caller-ID message are from the FSK-RAM, and the Start Bit/Stop Bit will be added automatically when sending the Caller-ID message.

The Flag Signal is a series of '1'. The length of the Flag Signal (Flag Length) is determined by the FL[7:0] bits in GREG13.

The BS (BT/Bellcore Selection) bit in GREG17 determines which specification the FSK generator will follow. The IDT821054 supports both Bellcore 202 and BT standards. Table - 1 is the comparison of these two standards.

Table - 1 BT/Bellcore Standard of FSK Signal

| Item                  | ВТ                                                                                                     | Bellcore                                                                                               |

|-----------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Mark (1)<br>frequency | 1300 Hz ± 1.5%                                                                                         | 1200 Hz ± 1.1%                                                                                         |

| Space (0) frequency   | 2100 Hz ± 1.1%                                                                                         | 2200 Hz ± 1.1%                                                                                         |

| Transmission rate     | 1200 baud ± 1%                                                                                         | 1200 Hz ± 1%                                                                                           |

| Word format           | 1 start bit which is '0', 8 word bits (with least significant bit LSB first), 1 stop bit which is '1'. | 1 start bit which is '0', 8 word bits (with least significant bit LSB first), 1 stop bit which is '1'. |

The MAS (Mark After Send) bit in GREG17 determines whether to keep on sending a series of '1's after the completion of sending the content in the FSK-RAM. If the total Caller-ID message is longer than 64 bytes, the MAS bit should be set to '1' to hold the link after the first 64 bytes of Caller-ID message have been sent. Then, users can update the FSK-RAM with new data and send the new data without re-sending the Seizure Signal and Mark Signal. This is important to keep the integrity of Caller-ID information.

The FCS[2:0] (FSK Channel Selection) bits in GREG17 are used to select one of the four channels to send the FSK signal. The FO bit GREG17 is used to enable/disable the FSK generator. When all configurations and FSK-RAM updating have been completed, the FS (FSK Start) bit in GREG17 should be set to '1' to trigger the sending of FSK signal. The FS bit will be reset to '0' after all data bytes in the FSK-RAM have been sent out.

A recommended procedure of programming the FSK generator is shown in Figure - 7.

Figure - 7 A Recommended Procedure of Programming the FSK Generator

#### 2.10 LEVEL METERING

The IDT821054 integrates a level meter which is shared by all 4 channels. The level meter is designed to emulate the off-chip PCM test equipment so as to facilitate the line-card, subscriber line and users telephone set monitoring. The level meter tests the return signal and reports the measurement result via the MPI interface. When combined with tone generation and loopbacks, it allows the microprocessor to test the channel integrity. The signal on the channel selected by the CS[1:0] bits in GREG21 will be metered.

The level meter is enabled by setting the LMO bit in GREG21 to '1'. A level meter counter register (GREG20) is used to set the value of time cycles for sampling the PCM data (8 kHz sampling rate). The output of level meter is sent to the level meter result registers GREG18 and

GREG19. The LVLL[7:0] bits in GREG18 contain the lower 7 bits of the result and a data-ready bit (LVLL[0]), while the LVLH[7:0] bits in GREG19 contain the higher 8 bits of the result. An internal accumulator sums the rectified samples until the value set in GREG20 is reached. By then, the LVLL[0] bit is set to '1' and accumulation result is latched into GREG18 and GREG19 simultaneously.

Once the higher byte of result (GREG19) is read, the LVLL[0] bit in GREG18 will be reset. It will be set to '1' again by a new data available. The contents of GREG18 and GREG19 will be overwritten by the following metering result if they have not been read out yet. To read the level meter result registers, it is recommended to read GREG18 (lower byte of result) first.

The L/C bit in GREG21 determines the level meter operation mode. If the L/C bit is '1', it means that metering mode is selected. In this mode,

the linear PCM data will be sent to the level meter and the metering result will be output to GREG18 and GREG19. With this result, the signal level can be calculated.

For A-law compressed PCM code or linear PCM code, the signal level can be calculated by the following formula:

$$A(dbm0) = 20 \times \log \left( \frac{LM_{Result} \times 2^5 \times \pi}{LM_{Countnumber} \times 2 \times 8192} \right) + 3.14$$

For  $\mu\text{-law}$  compressed PCM code, the signal level can be calculated by the following formula:

$$A(dbm0) = 20 \times log \left( \frac{LM_{Result} \times 2^5 \times \pi}{LM_{Countnumber} \times 2 \times 8192} \right) + 3.17$$

*LM*<sub>Result</sub>: the value in the level meter result registers (GREG18 & GREG19);

*LM*<sub>Countnumber</sub>: the count number of the level meter (set in GREG20).

If the L/C bit is '0', it means that message mode is selected. In this mode, the compressed PCM data will be output to GREG19 transparently without metering.

Refer to the Application Note for further details on the level meter.

#### 2.11 CHANNEL POWER DOWN/STANDBY MODE

Each individual channel of the IDT821054 can be powered down independently by setting the PD bit in LREG9 to '1'. If one channel is powered down and enters the standby mode, the PCM data transfer and the D/A, A/D converters of this channel will be disabled. In this way, the power consumption of the device can be reduced.

When the IDT821054 is powered up or reset, all four channels will be powered down. All circuits that contain programmed information retain their data after power down. The microprocessor interface is always active so that new commands can be received and executed.

#### 2.12 POWER DOWN/SUSPEND MODE

A suspend mode is provided for the whole chip to save power. The suspend mode saves much more power consumption than the standby mode. In this mode, the PLL block is turned off and the DSP operation is disabled. Only global and local commands can be executed, the RAM operation is disabled as the internal clock has been turned off. The PLL block is powered down by setting the PPD bit in GREG22 to '1'. Once the PLL and all four channels are powered down, the IDT821054 will enter the suspend mode.

#### 3 OPERATING THE IDT821054

#### 3.1 PROGRAMMING DESCRIPTION

The IDT821054 is programmed by writing commands to registers and coefficient RAM. A Channel Program Enable register (GREG6) is provided for addressing individual or multiple channels. The CE[3:0] bits in this register are assigned to Channel 4 to Channel 1 respectively. The channels are enabled to be programmed by setting their respective CE bits to '1'. If two or more channels are enabled, the successive write commands will be effective to all enabled channels. A broadcast mode can be implemented by simply enabling all four channels before performing other write-operation. The broadcast mode is very useful for configuring the coefficient RAM of the IDT821054 in a large system. But for read operations, multiple addressing is not allowed.

The IDT821054 uses an Identification Code to distinguish itself from other devices in the system. When being read, the IDT821054 will output an Identification Code of 81H first to indicate that the following data bytes are from the IDT821054.

#### 3.1.1 COMMAND TYPE AND FORMAT

The IDT821054 provides three types of commands as follows:

Local Command (LC), which is used to address the local registers of the specified channel(s).

Global Command (GC), which is used to address the global registers of all four channels.

RAM Command (RC), which is used to address the coefficient RAM (Coe-RAM) and FSK-RAM.

The format of the command is as the following:

| b7  | b6 | b5 | b4 | b3 | b2      | b1 | b0 |

|-----|----|----|----|----|---------|----|----|

| R/W | С  | T  |    |    | Address |    |    |

R/W: Read/Write Command bit

b7 = 0: Read Command

b7 = 1: Write Command

CT: Command Type

b6 b5 = 00: LC - Local Command b6 b5 = 01: GC - Global Command

b6 b5 = 10: Not Allowed

b6 b5 = 11: RC - RAM Command

Address: b[4:0], specify one or more local/global registers or a block

of Coe-RAM or FSK-RAM to be addressed.

For Local Command and Global Command, the b[4:0] bits are used to specify the address of the local registers and global registers respectively.

For the RAM Command, b4 is used to distinguish the Coe-RAM and the FSK-RAM:

b4 = 0: Command for addressing the Coe-RAM. The b[3:0] bits are used to address the blocks in the Coe-RAM.

b4 = 1: Command for addressing the FSK-RAM. The b3 bit is always '0' and the b[2:0] bits are used to address the blocks in the FSK-RAM.

#### 3.1.2 ADDRESSING THE LOCAL REGISTERS

When addressing the local registers, users must specify which channel(s) will be addressed first. If two or more channels are specified

via GREG6, the corresponding local registers of the specified channels will be addressed by a Local Command at the same time.

The IDT821054 provides a consecutive adjacent addressing method for accessing the local registers. According to the address specified in a Local Command, there will be 1 to 4 adjacent local registers to be addressed automatically, with the highest order first. For example, if the address specified in a Local Command ends with '11' (b1b0 = 11), 4 adjacent registers will be addressed by this command; if b1b0 = 10, 3 adjacent registers will be addressed. See Table - 2 for details.

Table - 2 Consecutive Adjacent Addressing

| Address Specified in a Local Command                      | In/Out Data<br>Bytes | Address of the Local Registers to be accessed |

|-----------------------------------------------------------|----------------------|-----------------------------------------------|

|                                                           | byte 1               | XXX11                                         |

| b[4:0] = XXX11                                            | byte 2               | XXX10                                         |

| (b1b0 = 11, four bytes of data)                           | byte 3               | XXX01                                         |

|                                                           | byte 4               | XXX00                                         |

| F14.01 - VVV40                                            | byte 1               | XXX10                                         |

| <b>b[4:0] = XXX10</b><br>(b1b0 = 10, three bytes of data) | byte 2               | XXX01                                         |

| (b) bo = 10, times bytes of data)                         | byte 3               | XXX00                                         |

| b[4:0] = XXX01                                            | byte 1               | XXX01                                         |

| (b1b0 = 01, two bytes of data)                            | byte 2               | XXX00                                         |

| <b>b[4:0] = XXX00</b> (b1b0 = 00, one byte of data)       | byte 1               | XXX00                                         |

When addressing local registers, the procedure of consecutive adjacent addressing can be stopped by the  $\overline{\text{CS}}$  signal at any time. If  $\overline{\text{CS}}$  is changed from low to high, the operation to the current register and the next adjacent registers will be aborted. However, the previous operation results will not be affected.

#### 3.1.3 ADDRESSING THE GLOBAL REGISTERS

For global registers are shared by all four channels, it is no need to specify the channel(s) before addressing a global register. Except for this, the global registers are addressed in a similar way as local registers. The procedure of consecutive adjacent addressing can be stopped by the  $\overline{\text{CS}}$  signal at any time.

#### 3.1.4 ADDRESSING THE COE-RAM

There are totally 40 words of Coe-RAM per channel. They are divided to 5 blocks. Each block consists of 8 words. Each word is 14-bit wide.

The 5 blocks of the Coe-RAM are assigned for different filter coefficients as shown below (refer to "9 Appendix: IDT821054 Coe-RAM Mapping" for the address of the Coe-RAM):

Block 1: IMF RAM (Word 0 - Word 7), containing the Impedance Matching Filter coefficient.

Block 2: ECF RAM (Word 8 - Word 15), containing the Echo Cancellation Filter coefficient.

Block 3: GIS RAM (Word 16 - Word 19) and Tone Generator RAM (Word 20 - Word 23), containing the Gain of Impedance Scaling and dual tone coefficients.

Block 4: FRX RAM (Word 24 - Word 30) and GTX RAM (Word 31), containing the coefficient of the Frequency Response Correction in Transmit Path and the Gain in Transmit Path:

Block 5: FRR RAM (Word 32 - Word 38) and GRX RAM (Word 39), containing the coefficient of the Frequency Response Correction in Receive Path and the Gain in Receive Path.

For the Coe-RAM is addressed on a per-channel basis, users should specify a channel (by setting the corresponding CE bit in GREG6 to '1') before writing/reading coefficients to/from the Coe-RAM.

To write a Coe-RAM word, 16 bits (b[15:0]) or two 8-bit bytes are needed to fulfill with MSB first, but the lowest two bits (b[1:0]) will be ignored. When read, each word will output 16 bits with MSB first, but the lowest two bits (b[1:0]) are meaningless.

The address in a Coe-RAM command (b[4:0]) specifies a block of Coe-RAM to be accessed. When a Coe-RAM command is executed, the CODEC automatically counts down from the highest address to the lowest address of the specified block. So all 8 words of the block will be addressed by one Coe-RAM command.

When addressing the Coe-RAM, the procedure of consecutive adjacent addressing can be stopped by the CS signal at any time. If the

CS signal is changed from low to high, the operation to the current word and the next adjacent words will be aborted. However, the previous operation results will not be affected.

#### 3.1.5 ADDRESSING FSK-RAM

The FSK-RAM consists of 4 blocks, and each block has 8 16-bit words. The total 32 words (i.e. 64 bytes) of FSK-RAM are shared by all four channels and only one channel can use it at one time.

To write a FSK-RAM word, 16 bits (or, two 8-bit bytes) are needed to fulfill with MSB first. When being read, each FSK-RAM word in FSK-RAM will output 16 bits with MSB first.

When addressing the FSK-RAM, the b3 bit in a FSK-RAM Command should be '0' and the b4 bit should be '1', the b[2:0] bits specify one of the 4 blocks of FSK-RAM. Then, all 8 words of the specified block will be addressed automatically, with the highest order word first.

#### 3.1.6 PROGRAMMING EXAMPLES

#### 3.1.6.1 Example of Programming Local Registers

#### • Writing to LREG2 and LREG1 of Channel 1:

1010, 0101 Channel Enable command

0001, 0010 Data for GREG6 (Channel 1 is enabled for programming)

1000, 0001 Local register write command (The address is '00001', which means that data will be written to LREG2 and LREG1.)

xxxx, xxxx Data for LREG2 xxxx, xxxx Data for LREG1

#### • Reading from LREG2 and LREG1 of Channel 1:

1010, 0101 Channel Enable command

0001, 0010 Data for GREG6 (Channel 1 is enabled for programming)

0000, 0001 Local register read command (The address is '00001', which means that LREG2 and LREG1 will be read.)

After the preceding commands are executed, data will be sent out as follows:

1000, 0001 Identification code

xxxx, xxxx Data read out from LREG2 xxxx, xxxx Data read out from LREG1

#### 3.1.6.2 Example of Programming Global Registers

#### · Writing to GREG1:

1010, 0000 Global register write command (The address is '00000', which means that data will be written to GREG1.)

1111, 1111 Data for GREG1

#### Reading from GREG1:

0010, 0000 Global register read command (The address is '00000', which means that GREG1 will be read.)

After the preceding command is executed, data will be sent out as follows:

1000, 0001 Identification code

0000, 0001 Data read out from GREG1

#### 3.1.6.3 Example of Programming the Coefficient-RAM

#### Writing to the Coe-RAM

1010,0101 Channel Enable command

0001,0010 Data for GREG6 (Channel 1 is enabled for programming)

1110,0010 Coe-RAM write command (The address of '00010' is located in block 3, which means that data will be written to block 3.)

data byte 1 high byte of word 8 of block 3

data byte 2 low byte of word 8 of block 3

data byte 3 high byte of word 7 of block 3

data byte 4 low byte of word 7 of block 3

data byte 5 high byte of word 6 of block 3

data byte 6 low byte of word 6 of block 3

data byte 7 high byte of word 5 of block 3

data byte 8 low byte of word 5 of block 3

```

data byte 9

high byte of word 4 of block 3 (see Note 1)

data byte 10

low byte of word 4 of block 3

data byte 11

high byte of word 3 of block 3

data byte 12

low byte of word 3 of block 3

data byte 13

high byte of word 2 of block 3

low byte of word 2 of block 3

data byte 14

data byte 15

high byte of word 1 of block 3

data byte 16

low byte of word 1 of block 3

```

Note 1: In block 3 of the Coe-RAM, word 5 to word 8 are used for tone coefficients while word 1 to word 4 are used for GIS coefficients. If users do not want to change the GIS coefficient while writing tone coefficients to the Coe-RAM, they can stop the procedure of consecutive adjacent addressing (after writing data to word 5) by pulling the CS signal to high, or they can rewrite word 1 to word 4 with the original GIS coefficients.

#### Reading from the Coe-RAM

|                 | **** *** * * * * * * * * * * * * * * * *                                                                    |

|-----------------|-------------------------------------------------------------------------------------------------------------|

| 1010,0011       | Channel Enable command                                                                                      |

| 0001,0010       | Data for GREG6 (Channel 1 is enabled for programming)                                                       |

| 0110,0010       | Coe-RAM read command (The address of '00010' is located in block 3, which means that block 3 will be read.) |

| After the prece | eding commands are executed, data will be sent out as follows:                                              |

| 1000,0001       | Identification code                                                                                         |

| data byte 1     | data read out from high byte of word 8 of block 3                                                           |

| data byte 2     | data read out from low byte of word 8 of block 3                                                            |

| data byte 3     | data read out from high byte of word 7 of block 3                                                           |

| data byte 4     | data read out from low byte of word 7 of block 3                                                            |

| data byte 5     | data read out from high byte of word 6 of block 3                                                           |

| data byte 6     | data read out from low byte of word 6 of block 3                                                            |

| data byte 7     | data read out from high byte of word 5 of block 3                                                           |

| data byte 8     | data read out from low byte of word 5 of block 3                                                            |

| data byte 9     | data read out from high byte of word 4 of block 3                                                           |

| data byte 10    | data read out from low byte of word 4 of block 3                                                            |

| data byte 11    | data read out from high byte of word 3 of block 3                                                           |

| data byte 12    | data read out from low byte of word 3 of block 3                                                            |

| data byte 13    | data read out from high byte of word 2 of block 3                                                           |

| data byte 14    | data read out from low byte of word 2 of block 3                                                            |

| data byte 15    | data read out from high byte of word 1 of block 3                                                           |

| data byte 16    | data read out from low byte of word 1 of block 3                                                            |

| 161 Evenn       | lo of Drogramming the ESK DAM                                                                               |

#### 3.1.6.4 Example of Programming the FSK-RAM

#### Writing to the FSK-RAM:

```

1111,0010

FSK-RAM write command (The address of '010' is located in block 3, which means that data will be written to block 3.)

data byte 1

high byte of word 8 of block 3

data byte 2

low byte of word 8 of block 3

data byte 3

high byte of word 7 of block 3

low byte of word 7 of block 3

data byte 4

data byte 5

high byte of word 6 of block 3

low byte of word 6 of block 3

data byte 6

data byte 7

high byte of word 5 of block 3

data byte 8

low byte of word 5 of block 3

data byte 9

high byte of word 4 of block 3

data byte 10

low byte of word 4 of block 3

data byte 11

high byte of word 3 of block 3

data byte 12

low byte of word 3 of block 3

data byte 13

high byte of word 2 of block 3

data byte 14

low byte of word 2 of block 3

data byte 15

high byte of word 1 of block 3

data byte 16

low byte of word 1 of block 3

Reading from the FSK-RAM:

```

0111,0010 FSK-RAM read command (The address of '010' is located in block 3, which means that block 3 will be read.)

After the preceding commands are executed, data will be sent out as follows:

1000,0001 Identification code

| data byte 1  | data read out from high byte of word 8 of block 3 |

|--------------|---------------------------------------------------|

| data byte 2  | data read out from low byte of word 8 of block 3  |

| data byte 3  | data read out from high byte of word 7 of block 3 |

| data byte 4  | data read out from low byte of word 7 of block 3  |

| data byte 5  | data read out from high byte of word 6 of block 3 |

| data byte 6  | data read out from low byte of word 6 of block 3  |

| data byte 7  | data read out from high byte of word 5 of block 3 |

| data byte 8  | data read out from low byte of word 5 of block 3  |

| data byte 9  | data read out from high byte of word 4 of block 3 |

| data byte 10 | data read out from low byte of word 4 of block 3  |

| data byte 11 | data read out from high byte of word 3 of block 3 |

| data byte 12 | data read out from low byte of word 3 of block 3  |

| data byte 13 | data read out from high byte of word 2 of block 3 |

| data byte 14 | data read out from low byte of word 2 of block 3  |

| data byte 15 | data read out from high byte of word 1 of block 3 |

| data byte 16 | data read out from low byte of word 1 of block 3  |

#### 3.2 POWER-ON SEQUENCE

To power on the IDT821054, users should follow the sequence below:

- 1. Apply ground first;

- 2. Apply VCC, finish signal connections and set the RESET pin to logic low. The device then goes into the default state;

- 3. Set the RESET pin to logic high;

- 4. Select master clock frequency;

- 5. Program filter coefficients and other parameters as required;

#### 3.3 DEFAULT STATE AFTER RESET

When the IDT821054 is powered on, or reset either by command or by setting the  $\overline{\text{RESET}}$  pin to logic low for at least 50  $\mu$ s, the device will enter the default state as follows:

- 1. All four channels are powered down and in standby mode.

- 2. All loopbacks and cutoff are disabled.

- 3. The DX1 pin is selected for all channels to transmit data and the DR1 pin is selected for all channels to receive data.

- 4. The master clock frequency is 2.048 MHz.

- Transmit and receive time slots are set to be 0-3 respectively for Channel 1-4. The PCM data rate is as same as the BCLK frequency. The PCM data is transmitted on rising edges of the BCLK signal and received on falling edges of it.

- 6. A-Law is selected.

- 7. The digital filters including GRX, FRR, GTX, FRX, GIS, ECF and IMF are disabled. The high-pass filters (HPF) are enabled. Refer to Figure 4 and descriptions on LREG1 for details.

- 8. The SB1, SB2 and SB3 pins are configured as inputs.

- 9. The SI1 and SI2 pins are configured as no debounce.

- 10. All interrupts are disabled and all pending interrupts are cleared.

- 11. All feature function blocks including FSK generator, dual tone generators, hardware ring trip and level meter are disabled.

- 12. The outputs of CHCLK1 and CHCLK2 are set to high.

The data stored in the RAM will not be changed by any kind of reset operations. So the RAM data will not be lost unless the device is powered down physically.

# 3.4 REGISTERS DESCRIPTION

### 3.4.1 REGISTERS OVERVIEW

Table - 3 Global Registers (GREG) Mapping

| Nama   | Function                                                                       |         |          | Register Byte |           |           |           |           |           |         | Write   | Default |

|--------|--------------------------------------------------------------------------------|---------|----------|---------------|-----------|-----------|-----------|-----------|-----------|---------|---------|---------|

| Name   | runction                                                                       | b7      | b6       | b5            | b4        | b3        | b2        | b1        | b0        | Command | Command | Value   |

| GREG1  | Version number (read)/<br>no operation (write)                                 |         |          |               |           |           |           |           |           | 20H     | АОН     | 01H     |

| GREG2  | Interrupt clear                                                                |         |          |               |           |           |           |           |           | -       | A1H     | _       |

| GREG3  | Software reset                                                                 |         |          |               |           |           |           |           |           | -       | A2H     | _       |

| GREG4  | Hardware reset                                                                 |         |          |               |           |           |           |           |           | _       | АЗН     | _       |

| GREG5  | Chopper clock selection                                                        | Rese    | erved    | CHclk2[1]     | CHclk2[0] | CHclk1[3] | CHclk1[2] | CHclk1[1] | CHclk1[0] | 24H     | A4H     | 00H     |

| GREG6  | MCLK selection and channel program enable                                      | CE[3]   | CE[2]    | CE[1]         | CE[0]     | Sel[3]    | Sel[2]    | Sel[1]    | Sel[0]    | 25H     | A5H     | 02H     |

| GREG7  | Data format,<br>companding law, clock<br>slope and PCM delay<br>time selection | А-µ     | VDS      | CS[2]         | CS[1]     | CS[0]     | OC[2]     | OC[1]     | OC[0]     | 26H     | A6H     | 00H     |

| GREG8  | SLIC ring trip setting and control                                             | OPI     | Reserved | IPI           | IS        | RTE       | OS[2]     | OS[1]     | OS[0]     | 27H     | A7H     | 00H     |

| GREG9  | Debounced data on SI1 and SI2 pins                                             | SIB[3]  | SIB[2]   | SIB[1]        | SIB[0]    | SIA[3]    | SIA[2]    | SIA[1]    | SIA[0]    | 28H     | -       | 00H     |

| GREG10 | SB1 direction control and SB1 data                                             | SB1C[3] | SB1C[2]  | SB1C[1]       | SB1C[0]   | SB1[3]    | SB1[2]    | SB1[1]    | SB1[0]    | 29H     | А9Н     | 00H     |

| GREG11 | SB2 direction control and SB2 data                                             | SB2C[3] | SB2C[2]  | SB2C[1]       | SB2C[0]   | SB2[3]    | SB2[2]    | SB2[1]    | SB2[0]    | 2AH     | AAH     | 00H     |

| GREG12 | SB3 direction control and SB3 data                                             | SB3C[3] | SB3C[2]  | SB3C[1]       | SB3C[0]   | SB3[3]    | SB3[2]    | SB3[1]    | SB3[0]    | 2BH     | ABH     | 00H     |

| GREG13 | FSK Flag Length                                                                | FL[7]   | FL[6]    | FL[5]         | FL[4]     | FL[3]     | FL[2]     | FL[1]     | FL[0]     | 2CH     | ACH     | 00H     |

| GREG14 | FSK Data Length                                                                | DL[7]   | DL[6]    | DL[5]         | DL[4]     | DL[3]     | DL[2]     | DL[1]     | DL[0]     | 2DH     | ADH     | 00H     |

| GREG15 | FSK Seizure Length                                                             | SL[7]   | SL[6]    | SL[5]         | SL[4]     | SL[3]     | SL[2]     | SL[1]     | SL[0]     | 2EH     | AEH     | 00H     |

| GREG16 | FSK Mark Length                                                                | ML[7]   | ML[6]    | ML[5]         | ML[4]     | ML[3]     | ML[2]     | ML[1]     | ML[0]     | 2FH     | AFH     | 00H     |

| GREG17 | FSK configuration                                                              | Rese    | erved    | FCS[1]        | FCS[0]    | FO        | BS        | MAS       | FS        | 30H     | ВОН     | 00H     |

| GREG18 | Level meter result low byte                                                    | LVLL[7] | LVLL[6]  | LVLL[5]       | LVLL[4]   | LVLL[3]   | LVLL[2]   | LVLL[1]   | LVLL[0]   | 31H     | _       | 00H     |

| GREG19 | Level meter result high byte                                                   | LVLH[7] | LVLH[6]  | LVLH[5]       | LVLH[4]   | LVLH[3]   | LVLH[2]   | LVLH[1]   | LVLH[0]   | 32H     | -       | 00H     |

| GREG20 | Level meter count number                                                       | CN[7]   | CN[6]    | CN[5]         | CN[4]     | CN[3]     | CN[2]     | CN[1]     | CN[0]     | 33H     | взн     | 00H     |

| GREG21 | level meter mode and<br>channel selection, level<br>meter enable               |         | Rese     | erved         |           | LMO       | L/C       | CS[1]     | CS[0]     | 34H     | В4Н     | 00H     |

| GREG22 | Loopback control and PLL power down                                            | Rese    | Reserved |               | DLB_ANA   | ALB_8k    | DLB_8k    | DLB_DI    | ALB_DI    | 35H     | B5H     | 00H     |

| GREG23 | Over-sampling timing tuning                                                    |         |          |               |           |           |           |           |           | 37H     | В7Н     | 00H     |

Table - 4 Local Registers (LREG) Mapping

|        |                                                               |          |         |         | Registe | er Byte |         |          |          | Read    | Write   |                                                          |

|--------|---------------------------------------------------------------|----------|---------|---------|---------|---------|---------|----------|----------|---------|---------|----------------------------------------------------------|

| Name   | Function                                                      | b7       | b6      | b5      | b4      | b3      | b2      | b1       | b0       | Command | Command | Default Value                                            |

| LREG1  | Coefficient selection                                         | CS[7]    | CS[6]   | CS[5]   | CS[4]   | CS[3]   | CS[2]   | CS[1]    | CS[0]    | 00H     | 80H     | 08H                                                      |

| LREG2  | Local loopbacks<br>control and SLIC input<br>interrupt enable | IE[4]    | IE[3]   | IE[2]   | IE[1]   | IE[0]   | DLB_PCM | ALB_1BIT | DLB_1BIT | 01H     | 81H     | 00Н                                                      |

| LREG3  | DSH and GK<br>debounce filters<br>configuration               | GK[3]    | GK[2]   | GK[1]   | GK[0]   | DSH[3]  | DSH[2]  | DSH[1]   | DSH[0]   | 02H     | 82H     | 00H                                                      |

| LREG4  | SLIC IO status/control data                                   | Reserved | SO2     | SO1     | SB3     | SB2     | SB1     | SI2      | SI1      | 03H     | 83H     | -                                                        |

| LREG5  | Transmit highway and time slot selection                      | THS      | TT[6]   | TT[5]   | TT[4]   | TT[3]   | TT[2]   | TT[1]    | TT[0]    | 04H     | 84H     | 00H for CH1<br>01H for CH2<br>02H for CH3<br>03H for CH4 |

| LREG6  | Receive highway and time slot selection                       | RHS      | RT[6]   | RT[5]   | RT[4]   | RT[3]   | RT[2]   | RT[1]    | RT[0]    | 05H     | 85H     | 00H for CH1<br>01H for CH2<br>02H for CH3<br>03H for CH4 |

| LREG7  | PCM data low byte                                             | PCM[7]   | PCM[6]  | PCM[5]  | PCM[4]  | PCM[3]  | PCM[2]  | PCM[1]   | PCM[0]   | 06H     | _       | 00H                                                      |

| LREG8  | PCM data high byte                                            | PCM[15]  | PCM[14] | PCM[13] | PCM[12] | PCM[11] | PCM[10] | PCM[9]   | PCM[8]   | 07H     | _       | 00H                                                      |

| LREG9  | Channel power down,<br>A/D and D/A gains,<br>PCM cutoff       | PD       | PCMCT   | GAD     | GDA     | 0       | 0       | 0        | 0        | 08H     | 88H     | 80H                                                      |

| LREG10 | Tone generator enable and tone program enable                 | Reserved |         |         |         | 1       | 1       | TEN1     | TEN0     | 09H     | 89H     | 00H                                                      |

For the global and local registers described below, it should be noted that:

- 1.  $\overline{R}/W = 0$ , Read command.  $\overline{R}/W = 1$ , Write command.

- 2. The reserved bit(s) in the registers must be filled in '0' in write operation and be ignored in read operation.

#### 3.4.2 GLOBAL REGISTERS LIST

#### GREG1: No Operation, Write (A0H); Version Number, Read (20H)

|         | b7  | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|---------|-----|----|----|----|----|----|----|----|

| Command | R/W | 0  | 1  | 0  | 0  | 0  | 0  | 0  |

By applying a read operation (20H) to this register, users can read out the version number of the IDT821054. The default value is 01H. To write to this register (no operation), a data byte of FFH must follow the write command (A0H) to ensure proper operation.

#### GREG2: Interrupt Clear, Write Only (A1H)

|         | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|---------|----|----|----|----|----|----|----|----|

| Command | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 1  |

All interrupts on SLIC I/O will be cleared by applying a write operation to this register. Note that a data byte of FFH must follow the write command (A1H) to ensure proper operation.

#### GREG3: Software Reset, Write Only (A2H)

|         | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|---------|----|----|----|----|----|----|----|----|

| Command | 1  | 0  | 1  | 0  | 0  | 0  | 1  | 0  |

A write operation to this register resets all local registers, but does not reset global registers and RAM. Note that when writing to this register, a data byte of FFH must follow the write command (A2H) to ensure proper operation.

#### GREG4: Hardware Reset, Write Only (A3)

CHclk1[3:0] = 0111:

|   |         | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|---|---------|----|----|----|----|----|----|----|----|

| ſ | Command | 1  | 0  | 1  | 0  | 0  | 0  | 1  | 1  |

A write operation to this register is equivalent to setting the RESET pin to logic low (Refer to "3.3 Default State After Reset" on page 21 for details). Note that when applying this write command, a data byte of FFH must follow to ensure proper operation.

#### GREG5: Chopper Clock Selection, Read/Write (24H/A4H)

|          | b7       | b6 | b5        | b4        | b3        | b2        | b1        | b0        |

|----------|----------|----|-----------|-----------|-----------|-----------|-----------|-----------|

| Command  | R/W      | 0  | 1         | 0         | 0         | 1         | 0         | 0         |

| I/O data | Reserved |    | Chclk2[1] | Chclk2[0] | Chclk1[3] | Chclk1[2] | Chclk1[1] | Chclk1[0] |

This register is used to select the frequency of the CHclk2 and CHclk1 output signals.

CHclk2[1:0] = 00: the output of chclk2 is set to high permanently (default);

CHclk2[1:0] = 01: chclk2 outputs a digital signal with the frequency of 512 kHz;

CHclk2[1:0] = 10: chclk2 outputs a digital signal with the frequency of 256 kHz;

CHclk2[1:0] = 11: chclk2 outputs a digital signal with the frequency of 16384 kHz;