# ELANC-PCI (TWISTED-PAIR ETHER-LAN CONTROLLER WITH PCI INTERFACE)

#### **GENERAL DESCRIPTION**

he ELANC-PCI (Twisted-pair Ether-LAN Controller with PCI Interface) integrates a W89C902 Serial(ELANC-PCI) LAN Coprocessor for Twisted-Pair (SLCT) and PC/AT PCI bus interface logic into a single chip. The ELANC-PCI provides an easy way of implementing the interface between an IEEE 802.3-compatible Ethernet and a personal computer, ELANC-PCI also provide fast DMA operation to improve the packet transmit and receive performance.

The PCI bus is a high performance local bus architecture with low latency random access time. It is a synchronous bus with operation up to 33MHz. The PCI bus interface is designed to provide the registers with the device information required for configuration, recording the status of the lines, control registers, interrupt line and I/O base address registers. It is capable of functioning in a half-duplex environment.

The W89C940F is designed to fully comply with the standard of PCI 2.0 specification. Taking advantage of PCI's nature, W89C940F supports auto-configuration function to free users' depression and confusion on tunning system resources conflict. With extremely high throughput on PCI bus, W89C940F offers a 32 bits data path to highly boost its performance without extra cost. Comparing with LAN card with ISA bus, its improvement is excellent. Besides, it also supports up to 256KB flash memory reserved for various applications, for instance anti-virus, popular drivers, Boot ROM, viewing your PC assets...etc., and what is more, these software are able to be updated on line. This can increase more niche feature on your LAN card, help you get more and bright your company profile. W89C940F is a single chip - build-in PCI bus interface and all necessary circuits - which will let design and board assembly become easy.

#### **FEATURES**

- Fully compatible with IEEE 802.3 standard

- Software compatible with Novell NE2000

- Complies with PCI Local Bus Specification Revision 2.0

- Slave Mode for PCI bus

- Fast DMA operation enhancing network access performance

- AUI, UTP interface available

- Supports one chip 32Kx8 and 16Kx8 SRAM

- Supports up to 64KB boot ROM

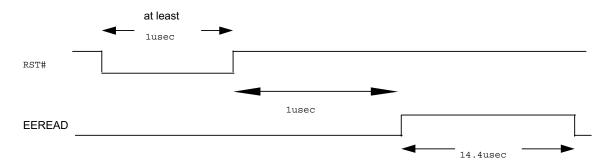

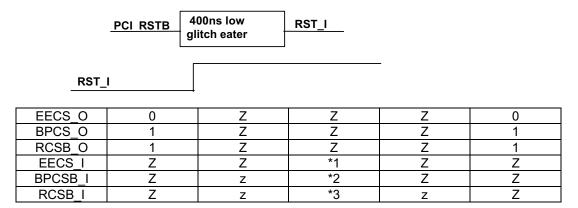

- EEPROM auto-load function after power on reset

- EEPROM on-board programming function available

- UTP interface polarity auto detection correction function available

- UTP/BNC auto media-switching function provided

- LED displaying for network segment Link/activity status

- Signature register available for device identification

- Single 5V power supply with low power consumption

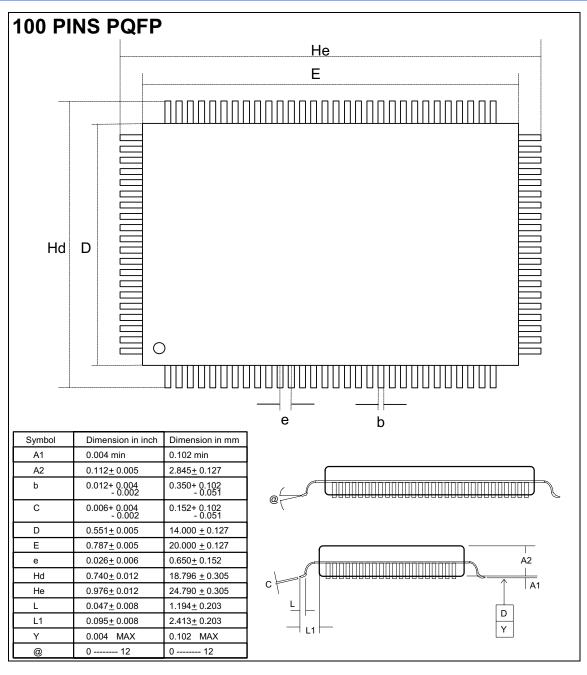

- 100 Pin PQFP

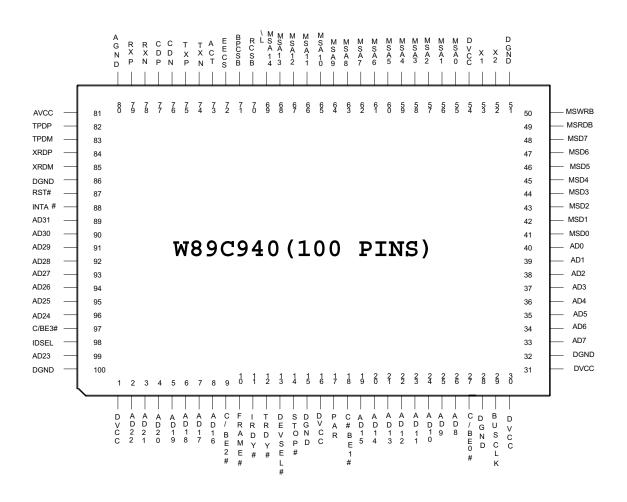

## **PIN CONFIGURATION**

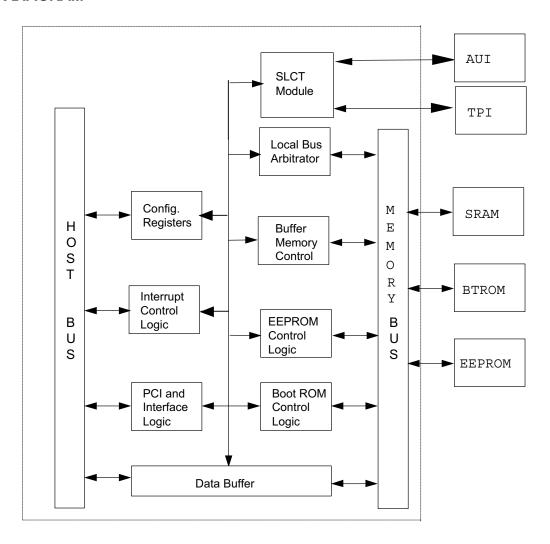

## **BLOCK DIAGRAM**

## **PIN DESCRIPTION**

|                                      | PCI INTERFACE                     |       |                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|--------------------------------------|-----------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                                 | NUMBER                            | TYPE  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| CLK                                  | K 29 in                           |       | Clock:                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                                      |                                   |       | Bus clock from PCI bus. All of the PCI signals, except RST#, are synchronized by rising edge of clock.                                                                                                                                                                                                                                                                                                             |  |  |

|                                      |                                   |       | The allowable operating frequency of CLK for W89C940 is from 25MHz to 33MHz.                                                                                                                                                                                                                                                                                                                                       |  |  |

| RST#                                 | 87                                | in    | Reset:                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                                      |                                   |       | Asynchronous reset signal from PCI bus.                                                                                                                                                                                                                                                                                                                                                                            |  |  |

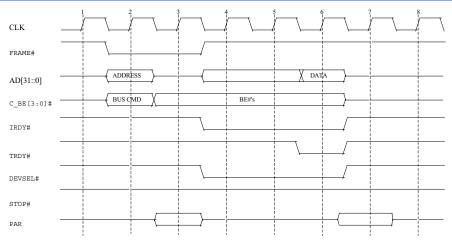

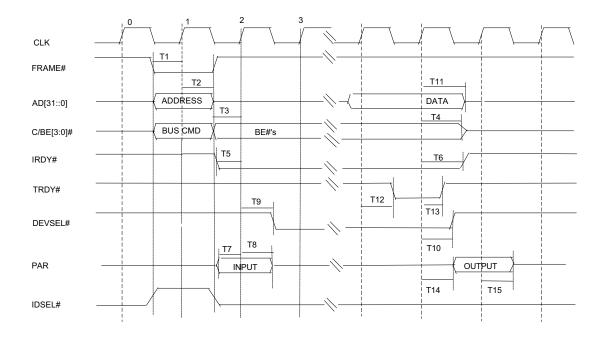

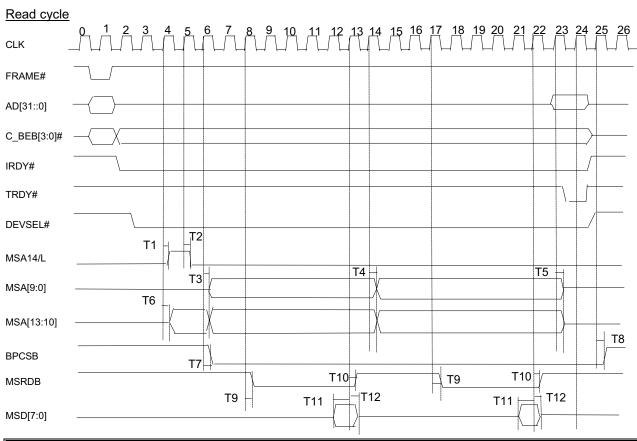

| AD[31:00]                            | 00 00                             | t/s   | Address and Data:                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| AD31-<br>AD24<br>AD23<br>AD22-       | 89 - 96<br>99<br>2 - 8<br>19 - 26 |       | Bidirection bus for PCI address and data signals transaction. AD[31:00] is a time division bus. Two phases are used to carry the address and data messages of PCI bus. The address phase is the clock cycle in which FRAME# is aeerted.                                                                                                                                                                            |  |  |

| AD16<br>AD15-AD8                     | 33 - 40                           |       | AD[31:24] contains the most significant byte(MSB) and the AD[7:0] contain the least significant byte(LSB) during the data phase.                                                                                                                                                                                                                                                                                   |  |  |

| AD7-AD0                              |                                   |       | The data written from host should be stable and valid when IRDY# is asserted. The data driven by W89C940 will be stable and valid when TRDY# is asserted.                                                                                                                                                                                                                                                          |  |  |

| C/BE[3:0]#                           | 07                                | t/s   | Bus Command and Byte Enables:                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| C/BE3#<br>C/BE2#<br>C/BE1#<br>C/BE0# | /BE1# 18                          |       | C/BE[3:0]# define the type of bus command during the address phase and the byte enables during the data phase of a transaction. There are 16 types of bus command defined in PCI bus. Four bits of C/BE[3:0]# are used to decode the 16 types of bus command. The byte enable determine which byte lanes carry meaningful data.                                                                                    |  |  |

|                                      |                                   |       | C/BE0# indicate the byte 0(AD[7:0]) is valid. C/BE1# indicate the byte 1(AD[15:8]) is valid. C/BE2# indicate the byte 2(AD[23:16]) is valid. C/BE3# indicate the byte 3(AD[32:24]) is valid.                                                                                                                                                                                                                       |  |  |

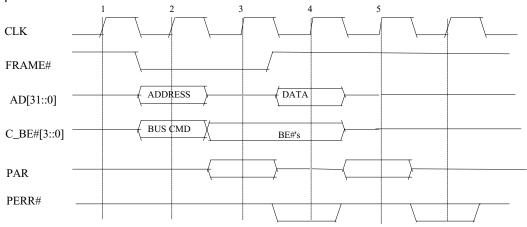

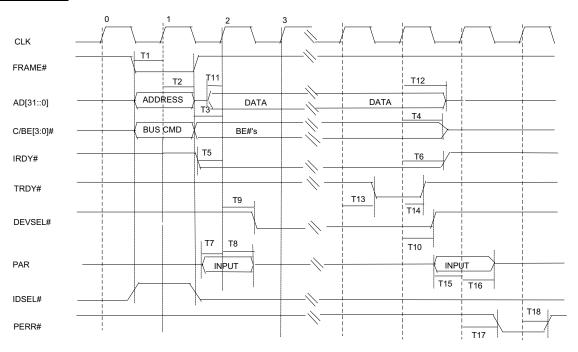

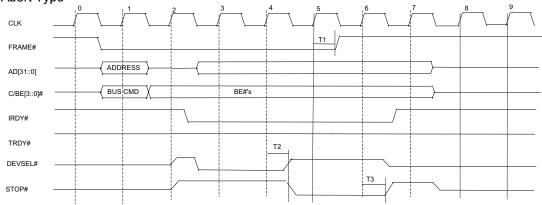

| PAR                                  | 17                                | t/s   | Parity:                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                                      |                                   |       | Even parity across AD[31:0] and C_BE[3:0]B.                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                                      |                                   |       | W89C940 will drive the PAR in read data phase. The host drives the PAR for address phase and writes data phase. PAR is stable and valid one clock after the address phase. PAR is stable and valid one clock after either IRDY# is asserted on a write transaction or TRDY# is asserted on a read transaction. Once PAR is valid, it remains valid until one clock after the completion of the current data phase. |  |  |

| FRAME#                               | 10                                | s/t/s | Cycle Frame:                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                                      |                                   | in    | FRAME# is asserted by host to indicate the beginning of a bus transaction. When FRAME# is deasserted, the transaction is in the final data phase.                                                                                                                                                                                                                                                                  |  |  |

|         | PCI INTERFACE |       |                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|---------|---------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME    | NUMBER        | TYPE  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| IRDY#   | 11            | s/t/s | Initiator Ready:                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|         |               | in    | Initiator Ready indicates the host's ability to complete the current data phase of transaction. During a write cycle, IRDY# indicates that valid data is presented on AD[31:00]. During a read cycle, it indicates the master is ready to accept the data. The wait cycles are inserted till IRDY# and TRDY# are asserted at the same cycle.       |  |  |  |

| TRDY#   | 12            | s/t/s | Target Ready:                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|         |               |       | Target Ready indicates the W89C940's ability to complete the current data phase of transaction. During a read cycle, TRDY# indicates that valid data is presented on AD[31:00]. During a write cycle, it indicates the W89C940 is ready to accept the data. The wait cycles are inserted till both IRDY# and TRDY# are asserted at the same cycle. |  |  |  |

| STOP#   | 14            | s/t/s | STOP:                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|         |               |       | Stop indicates W89C940 is requesting the master to stop the current transaction.                                                                                                                                                                                                                                                                   |  |  |  |

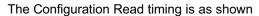

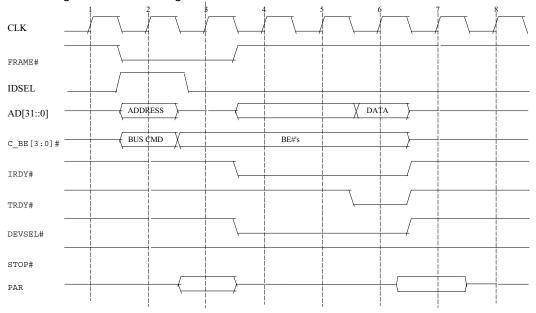

| IDSEL   | 98            | in    | Initialization Device Select:                                                                                                                                                                                                                                                                                                                      |  |  |  |

|         |               |       | IDSEL is used as a chip select during PCI configuration read and write transaction.                                                                                                                                                                                                                                                                |  |  |  |

| DEVSEL# | 13            | s/t/s | Device Select:                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|         |               |       | DEVSEL# will be asserted when W89C940 decode the correct address.                                                                                                                                                                                                                                                                                  |  |  |  |

| INTA#   | 88            | o/d   | Interrupt Request:                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|         |               |       | INTA# is used to request an interrupt service. The interrupt signal can be masked by the register of IMR( Interrupt Mask Register). INTA# status is kept at ISR( Interrupt Status Register).                                                                                                                                                       |  |  |  |

|            | NETWORK INTERFACE |                |                                                                                                                                                                                                                                             |  |

|------------|-------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME       | NUMBER            | TYPE           | DESCRIPTION                                                                                                                                                                                                                                 |  |

| X1<br>X2   | 53<br>52          | I/TTL<br>O/TTL | Crystal or Oscillator Input. Crystal or oscillator input (X1) and output (X2) pin. If a crystal is used, it should be connected directly to X1 and X2. If an oscillator is selected, X1 is the 20 MHz input and X2 should be left floating. |  |

| TXP<br>TXN | 75<br>74          | O/AUI          | AUI Transmit Output:                                                                                                                                                                                                                        |  |

|              | NETWORK INTERFACE |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                     |  |  |

|--------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME         | NUMBER            | TYPE                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DESCRIPTION                                                                                                                                                                                                                         |  |  |

| RXP<br>RXN   | 79<br>78          | I/AUI                                                                                                                                                                                                                                                                                                                                                                                                                                                   | AUI Receive Input: AUI differential input pair. The data received by network transceiver will be sent back through RXP and RXN in a differential signal format. The RXP and RXN are also should be isolated by a pulse transformer. |  |  |

| CDP<br>CDN   | 77<br>76          | I/AUI                                                                                                                                                                                                                                                                                                                                                                                                                                                   | AUI Collision Input:  AUI differential input pair. The network transceiver will drive a 10MHz differential signal onto CDP and CDN when a collision event is occurred. The CDP and CDN should be isolated by a pulse transformer.   |  |  |

| XRDP<br>XRDM | 84<br>85          | I/TPI                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TPI Receive Input:  10BASE-T receive differential input pair. RXP and RXN should be shunted by a 100 ohms resistor for twisted-pair line impedance matching.                                                                        |  |  |

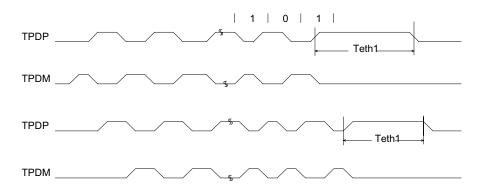

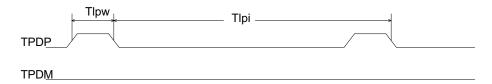

| TPDP<br>TPDM | 82<br>83          | O/TPI                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TPI Transmit Output:  10BASE-T transmit differential output pair. A 1.21K ohm shunt resistor is required across the TXP and TXN for signal pre-equalization.                                                                        |  |  |

| ACT          | 73                | O/LED Activity Displaying:  Network activity displaying. ACT will indicate the network activity status by types of signals(DC 0 , DC1 and AC 10Hz).  DC 0 : indicating "Link Good", if UTP is selected.  DC 1 : indicating 1) "Link fail", if UTP is selected.  2) "idle", if AUI is selected.  AC 10HZ : indicating the DTE is transmitting a packet or the carrier on the network is detected by the transceiver and the carrier sense signal is reco |                                                                                                                                                                                                                                     |  |  |

|              |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | by W89C940.  The ACT will keep DC 1 if there is an abnormal network collision occurred, f.g. the transceiver collision signal always active.                                                                                        |  |  |

| MEMORY INTERFACE |         |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|------------------|---------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME             | NUMBER  | NUMBER TYPE DESCRIPTION |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| MSD[7:0]         | 48 - 41 | B/MOS                   | Local Memory Data Bus:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                  |         |                         | A bidirection bus for data transfer between the local memory and the W89C940.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

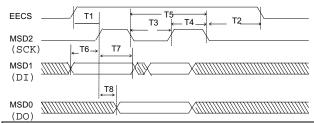

|                  |         |                         | MSD0 is used as a serial data input pin during the auto configuration duration for hardware reset. The data drove by the DO of EEPROM will clocked into the MSD0 when the EEPROM load operation is active. The Ethernet node ID and optional configuration content will be loaded into chip segisters at this moment. MSD1 is used as a serial data output pin during the auto configuration duration for hardware reset. The command drove by the MSD1 will be clocked into the DI of EEPROM for accessing the content of EEPROM. MSD2 supplies the clock with a period of 1.2 μS for EEPROM during auto configuration duration. |  |  |  |

|           | MEMORY INTERFACE |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|-----------|------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME      | NUMBER           | TYPE  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

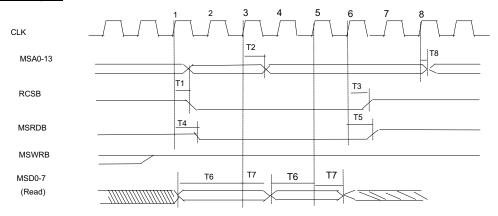

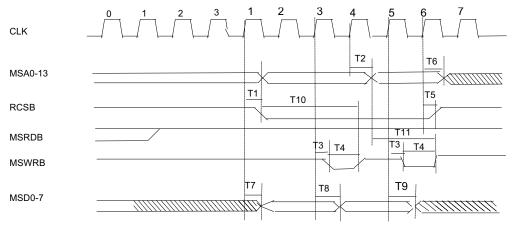

| MSRDB     | 49               | O/MOS | Local Memory Read Enable.  An active low signal to enable the local SRAM read.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| MSWRB     | 50               | O/MOS | Local Memory Write Enable. An active low signal to enable the local SRAM write.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| MSA[14:0] | 69 - 55          | O/MOS | Local Memory Address Bus. Address bus for local memory addressing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|           |                  |       | The MSA14 will be used as the address strobe signal when the size is larger than 32Kx8. If the ROM size is larger than 32Kx8, Boot ROM address !13-A10 is connected to MSA13-MSA10 and A17-A14 is connected to the latched MSA13-MSA10. The valid address for the higher significant bits(A14,A15,) will be stable before the BPCSB is active low and should be latched by an external data latch which is triggered by MSA14. The A0 ~ A13 of the BOOT ROM device are connected to MSA0 ~ MSA13 directly no matter the BOOT ROM size is larger than 32Kx8 or not. |  |  |  |

| RCSB      | 70               | O/MOS | Memory Chip Select:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|           |                  |       | The RCSB is active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|           |                  |       | RCSB enables the local memory read/write cycle in conjunction with the MSRDB, MSWRB pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| BPCSB     | 71               | O/MOS | BOOT ROM Chip Select:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|           |                  |       | BPCSB is active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|           |                  |       | BPCSB enables the BOOT ROM read cycle during the system booting up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| EECS      | 72               | O/MOS | EEPROM Chip Select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|           |                  |       | The EEPROM read/write operation will be enabled when EECS is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| POWER PINS                   |                                                               |   |                                                          |  |

|------------------------------|---------------------------------------------------------------|---|----------------------------------------------------------|--|

| NAME NUMBER TYPE DESCRIPTION |                                                               |   |                                                          |  |

| DVCC                         | 1, 16, 30,                                                    | I | Digital Power Supply:                                    |  |

|                              | 31, 54                                                        |   | 5V DC power supply for internal digital logic circuitry. |  |

| DGND 15, 28, 32,             |                                                               | I | Digital Ground:                                          |  |

|                              | 51, 86, 100 Ground pins for internal digital logic circuitry. |   | Ground pins for internal digital logic circuitry.        |  |

| AVCC 81 I                    |                                                               | I | Analog Power Supply:                                     |  |

|                              |                                                               |   | 5V DC power supply for internal analog circuitry.        |  |

| POWER PINS                   |                                                                                                                                                                                     |                  |  |  |  |  |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|--|--|--|

| NAME NUMBER TYPE DESCRIPTION |                                                                                                                                                                                     |                  |  |  |  |  |

| AGND                         | 80                                                                                                                                                                                  | I Analog Ground: |  |  |  |  |

|                              | Ground pin for internal analog circuitry.                                                                                                                                           |                  |  |  |  |  |

|                              | It is recommended that there is a decoupling capacitor connected between power supply pins and ground pins. A RC low pass filter is also recommend be used for analog power supply. |                  |  |  |  |  |

Note: Signal Type Definition

in Input is a standard input-only signal

out Totem Pole output is a standard active driver.

t/s Tri-State is a bi-directional, tri-state input/output pin.

s/t/s Sustained Tri-State is an active low tri-state signal owned and driven by one and only one agent at a time. The agent that drives an s/t/s pin low must drive it high for at least one clock before letting it float. A new agent cannot start driving a s/t/s signal any sooner than one clock after the previous owner tri-states it. A pull-up is required to sustain the inactive state until another agent drives it, and must be provided by the central resource.

o/d Open Drain allows multiple devices to share as a wire-OR.

#### **FUNCTIONAL DESCRIPTION**

#### **IEEE 802.3 MAC FUNCTION**

#### Core Coprocessor (SLCT) Operation

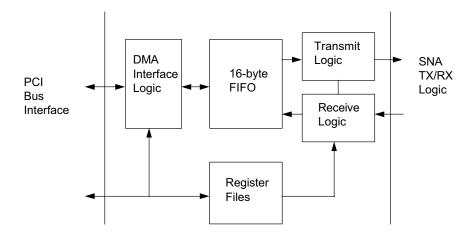

The SLCT core coprocessor has five major logic blocks that control Ethernet operations: the register files, transmit logic, receive logic, FIFO logic, and DMA logic. The relationship between these blocks is depicted in the following block diagram.

## Register Files

The register files of the SLCT can be accessed in the same way as the configuration registers. The ELANC-PCI should be in slave mode when the system accesses the register files. The command register (CR) determines the page number of the register file, while the system address SA<0:3> selects one register address from 01H to 0fH. The PCI IO read/write commands are used to activate the I/O operations. Refer to the W89C90 data sheet for more detailed information on the registers.

#### **DMA Interface Logic**

The SLCT has two types of DMA operations, local DMA and remote DMA.

#### FIFO Logic

The SLCT has a 16-byte FIFO, which acts as an internal buffer to adjust transmission/reception speed differences between DMAs. The FIFO has FIFO threshold pointers to determine the level at which it should initiate a local DMA. The threshold levels are different for reception and transmission. The FIFO threshold levels are defined in the DCR register.

The FIFO logic also provides a FIFO overrun and underrun signal for network management purposes. In a case where the receive packets are flooding into the FIFO but the SLCT still does not have the bus authority, the FIFO may be overrun. On the other hand, if a transmission begins before data are fed into the FIFO, it may be underrun. Both cases result in a network error. These types of cases can be prevented by changing the values of the FIFO thresholds.

Normally, the data in the FIFO cannot be read; reading FIFO data during normal operation may cause the system to hang. In loopback mode, however, the SLCT allows FIFO data to be read by byte in order to check the correctness of the loopback operation.

#### Receive Logic

The receive logic is responsible for receiving the serial network data and packing the data in byte/word sequence. The receive logic thus has serial to parallel logic in addition to network detection capability.

The ELANC-PCI accepts both physical addresses and group addresses (multicast and broadcast addresses). The SLCT extracts the address field from the serial input data. It then determines if the address is acceptable, according to the configurations defined in the receive configuration register (RCR). If the address is not acceptable, the packet reception is aborted. If the address is acceptable, the data packet is sent to the serial to parallel logic before being fed into the FIFO. Data packets can thus be processed either byte or word-wide.

After receiving a data packet, the SLCT automatically adds four bytes of data receive status, next packet pointer, and two bytes of receive byte count into the FIFO for network management purposes. The receive status contains the status of the incoming packet, so that the system can determine if the packet is desired. The next packet pointer points to the starting address of the next packet in the local receive ring. The receive byte count is the length of the packet received by the SLCT. Note that the receive byte count may be different from the "length" field specified in the Ethernet packet format. These four bytes of data will be transferred to the local buffer with the last batch of the local DMA. However, these four bytes are stored at the first four addresses before the packet.

#### Transmit Logic

The SLCT must be filled before transmission begins. That is, the local DMA read must begin before the SLCT begins transmission. The SLCT first transmits 62 bits of preamble, then two bits of SFD, and then the data packet. The parallel to serial logic serializes the data from the FIFO into a data packet. After the data packet, the SLCT optionally adds four bytes of cyclic redundancy code (CRC) to the tail of the packet.

A protocol PLA determines the network operations of the ELANC-PCI. Collision detection, random backoff, and auto retransmit are implemented in the transmit logic. The protocol PLA ensures that the ELANC-PCI follows IEEE 802.3 protocol.

#### 10BASE2 AND 10BASE5 PLS (PHYSICAL LAYER SIGNAL) FUNCTION

#### **SNA Operation**

#### File 1

The ELANC-PCI also contains a Serial Network Adapter (SNA), which adapts the Non-Return-to-Zero (NRZ) used in the core processor and host system to Manchester coded network symbols.

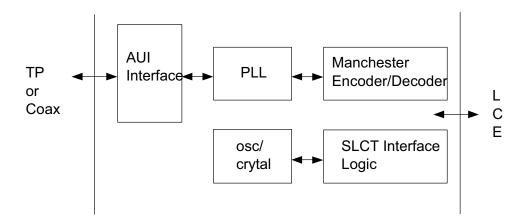

The SNA contains three blocks: a Phase Locked Loop (PLL), a Manchester encoder/decoder, and a collision decoder, as well as crystal/oscillator logic.

The Manchester encoder/decoder handles code interpretation between NRZ signals and Manchester coded signals. The PLL locks the receiving signals with an internal voltage control oscillator (VCO) so that network noise(jitter) can be eliminated before the signals enter the core coprocessor. The collision decoder detects whether the network is in a collision status.

#### **10BASE-T MAU FUNCTION**

#### **TP Transceiver Operation**

#### **Transmit Driver**

There are two signals for data transmission, TXP and TXN, which connect to the twisted-pair cable via a transmitter filter and an optional common mode choke.

#### **Smart Squelch**

The main function of this block is to determine when valid data are present on the differential receiving inputs (RXP/RXN). To ensure that impulse noise on the medium will not be taken as a valid datum, this circuit adopts a combination of amplitude and timing measurements to determine the validity of the input signals. To qualify incoming data, the smart squelch circuitry monitors the signals for three peaks of alternating polarity that occur within a 400 nS window. Once this condition has been satisfied, the squelch level is reduced to minimize the noise effect and the chances of causing premature Start Of Idle (SOI) pulse detection. If the receiver detects activity on the receive line while packets are being transmitted, incoming data is qualified on five peaks of alternating polarity so as to prevent false collisions caused by impulse noise. The squelch function returns to its squelch state under any of the following conditions:

- -A normal Start Of Idle (SOI) signal

- An inverted SOI signal

- A missing SOI signal

A missing SOI signal is assumed when no transitions have occurred on the receiver for 175nS after a packet has arrived. In this case, a normal SOI signal is generated and appended to the data.

#### Collision Detection

A collision occurs when transmit and receive signals occur simultaneously on the twisted pair cable. Collisions will not be reported when the device is in link-fail state. The collision signal is also generated when the transceiver has detected a jabber condition or when the SQE test is being performed.

#### SQE test

The Signal Quality Error (SQE) test is used to test the collision signaling circuitry in the Twisted Pair Transceiver module. After each packet transmission, an SQE signal is sent to the SLCT. The SLCT expects this signal and will flag an error if it does not exist.

#### Jabber

The jabber timer monitors the transmitter and disables the transmission if the transmitter is active for greater than 26.2 mS.The jabber will re-enable the transmitter after the SLCT has been idle for at least 420 mS.

#### Link Integrity

During periods of inactivity, link pulses are generated and received by both MAUs at either end of the twisted pair to ensure that the cable has not been broken or shorted. A positive, 100 nS Link Integrity signal is generated by the Twisted Pair Transceiver and transmitted on the twisted pair cable every 13 ms during periods of no transmission activity. The ELANC-PCI assumes a link-good state if it senses valid link pulse activity on the Twisted Pair Transceiver receive circuit. If neither receive data nor a link pulse (positive or negative) is detected within 105 mS, the ELANC-PCI enters link-fail state. When a link-fail condition occurs, four consecutive positive link pulses (or eight negative link pulses) must be received before a link-good condition is assumed.

#### LCE CORE ACCESS FUNCTION

### LCE core access function (LCE: Lan Controller of Ethernet)

The LCE core of the ELANC-PCI can be accessed by programming the register of the LCE core. The ELANC-PCI's register files are mapped into the lower 16 I/O spaces: iobase to iobase+0FH. Any read/write to the ELANC-PCI's registers is an "IN"/"OUT" command to these addresses.

Addresses iobase+10H to iobase+17H are mapped to the I/O port for the system to access the contents of the buffer memory. Remote DMA reads and writes correspond to "IN"/"OUT" commands to these addresses.

When addresses iobase+18H to +1FH are read a software reset will be issued to the core coprocessor and released about 780nsec later, automatically.

The following table summarizes the I/O address mapping:

| ADDRESS                 | REGISTER             | OPERATION                 |  |

|-------------------------|----------------------|---------------------------|--|

| iobase+00H - iobase+0FH | LCE core's registers | Slave register read/write |  |

| iobase+10H - iobase+17H | I/O Ports            | Remote DMA read/write     |  |

| iobase+18H - iobase+1FH | Reset                | Software reset            |  |

The buffer memory map for LCE core memory address space is summarized in the following table:

| NE2000 COMPATIBLE              |                      |  |  |

|--------------------------------|----------------------|--|--|

| 0000H - 001FH                  | ID Registers         |  |  |

| 0020H - 00FFH<br>0100H - 3FFFH | Unused               |  |  |

| 4000H - 7FFFH                  | 16K X 8 local memory |  |  |

| 8000H - FFFFH                  | Unused               |  |  |

#### NODE ID

Each node in an Ethernet network has a unique six-byte ID. The node ID is mapped into the memory space of the ELANC-PCI. The ELANC-PCI will load the node ID from the EEPROM after power on reset. The node I.D. should be allocated in the first 3 words(with the address of 00H ~ 02H) of the EEPROM.

#### **Bus Arbitration**

The ELANC-PCI handles bus arbitration automatically. The LAN card can operate in four modes: idle state, slave read/write mode, DMA mode, and PCI mode. The ELANC-PCI controls the on-board devices by decoding these modes.

At power on, the ELANC-PCI is in idle mode. If a register read/write command is issued, the ELANC-PCI enters the slave read/write mode. If a local DMA or remote DMA is initiated by the ELANC-PCI core coprocessor, the ELANC-PCI enters DMA mode. A PCI command will put the ELANC-PCI into PCI mode. At any given time, the ELANC-PCI can be in only one state. The ELANC-PCI handles state changes automatically. However, two events, such as a DMA command and an PCI command, may be requested at the same time; in this case, the ELANC-PCI allocates the bus on a first-come, first-served basis. No predefined priority is set within the ELANC-PCI.

#### **NE2000 MODE DMA FUNCTION**

The ELANC-PCI provides two DMA channels for system access. The remote DMA mode moves data between system memory space and local memory space. The local DMA moves data between the FIFO of the SLCT and local memory space. However, since the SLCT can handle local DMA operations without system intervention (refer to the data sheet for the SLCT), the system has to perform only remote DMA reads/writes.

In a transmit operation, the data should be moved to local memory before the system orders the SLCT to start transmission. The remote DMA write moves the data from the PCI bus to the local SRAM. This is simply an "OUT" command on the PC. For a receive operation, the network may feed data constantly and the local memory may become full if the data are not moved out to system memory through a remote DMA read operation. This operation is the "IN" command on the PC.

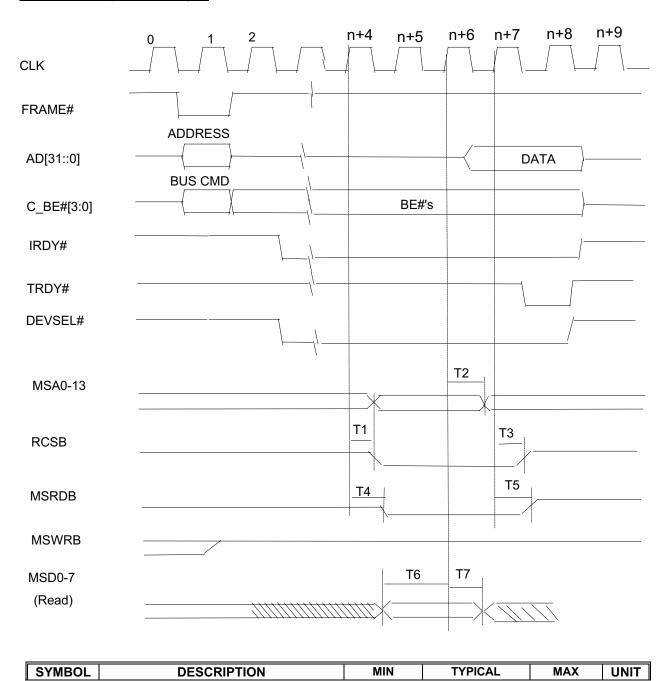

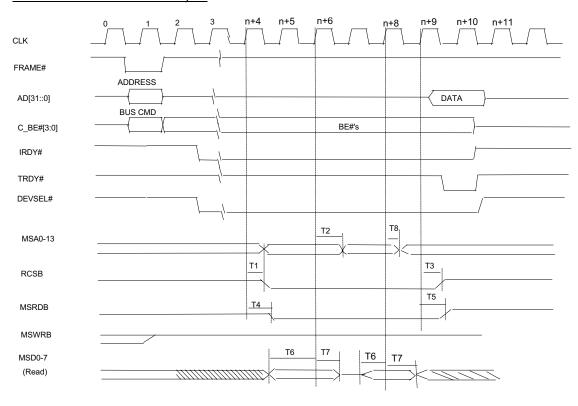

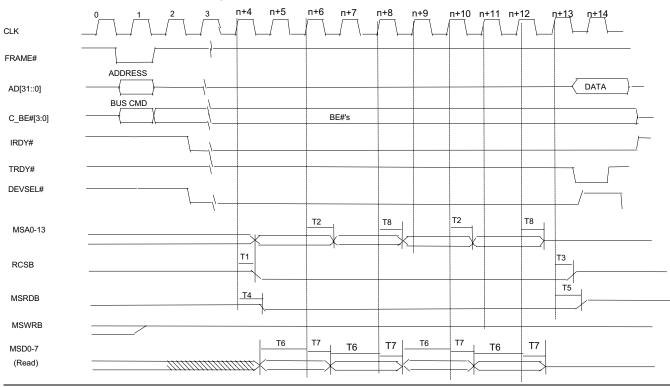

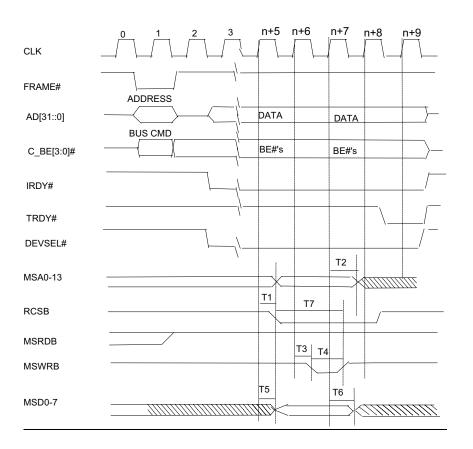

#### Remote DMA

A remote DMA can be performed only in I/O mode. The remote DMA moves data between the host and the local buffers. Unlike a local DMA, the remote DMA is byte or word-wide. Each remote DMA operation transfers four bytes, double-word, depending on the PCI cycle.

Since the remote DMA is simply an PCI I/O operation, PCI is sometimes affected by a remote DMA. If the remote DMA is interleaved with other devices, TRDY# is deasserted to force the system to insert wait states. The ELANC-PCI will automatically handle any arbitration necessary.

A Double word access on W89C940 from PCI bus is allowed. The buffer memory access will stop when the Remote Byte Counter is decreased to zero. A double word read command will read only three bytes of valid data if remote byte counter is set 3 or two bytes of valid data if the remote byte counter is set 2 respectively.

#### Local DMA

The local DMA transfers data from/to the on-board buffers. To perform data reception or transmission from/to remote nodes in the network, data must be moved from/to the FIFO. To enhance the efficiency of the transmission, the local DMA transfers data in batches: Data are first collected and then moved in a batch. Each transfer can move up to 12 bytes of data at once. This scheme reduces time wasted in requesting the bus.

A local DMA begins by requesting the local bus. If the bus is available to the ELANC-PCI, it responds at once by asserting the bus acknowledge; if, on the other hand, the bus is currently authorized to another device, the ELANC-PCI will not assert the bus acknowledge and the SLCT must wait. Note that this sequence will not affect the host system or the PCI bus signals. After each batch is transferred, the SLCT checks the FIFO threshold levels to determine if another batch transfer should be requested.

#### **BOOT PROM ACCESS FUNCTION**

#### **Boot PROM Operation**

For diskless applications, the system requires an on-board boot device. The ELANC-PCI allows the system to use an on-board BOOT PROM as the boot device.

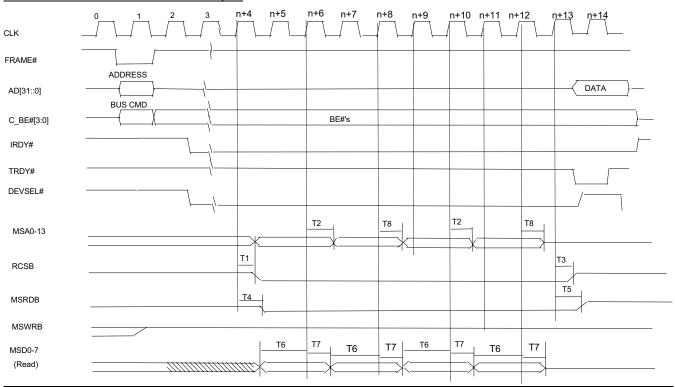

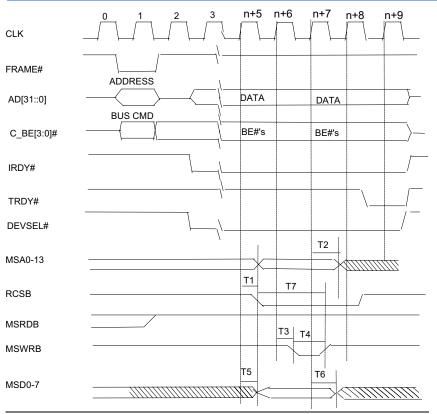

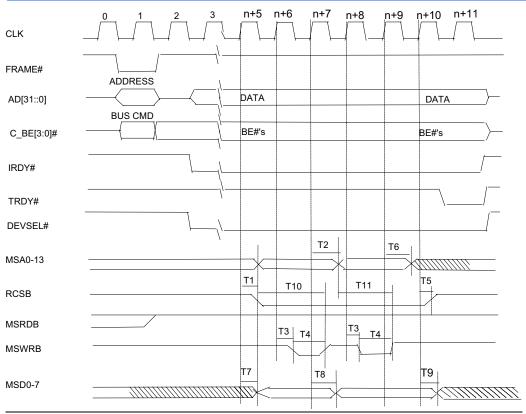

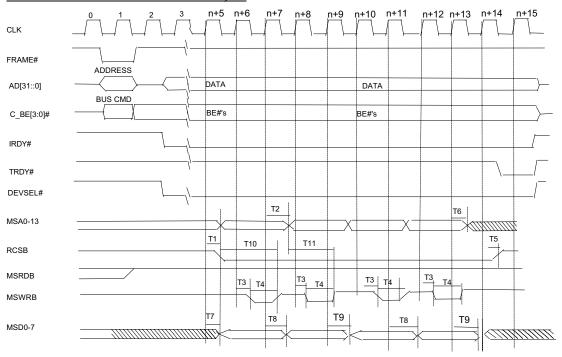

The BOOT PROM is essentially a byte-read device. ELANC-PCI will fetch a byte from the BOOT PROM and drive the AD bus of the PCI Interface. If the system do a word read command, the ELANC-PCI will invoke two byte read operation with consecutive address and drove the second byte on another byte of the PCI interface. For double word command, the ELANC-PCI will deassert the TRDY# until four read operation with consecutive address to the BOOT PROM is completed and then the four bytes of data will be drove onto the 32 bits data bus of PCI.

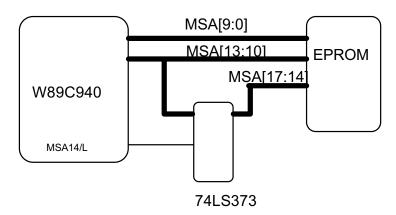

W89C940 can support the EPROM and Flash memory with 220nsec access time with the size up to 256KB. In order to support 64KB,128KB and 256KB size with 15-bit address bus, W89C940 use MSA14 to latch the high address bits MSA[17:14] from MSA[13:10]. The structure for address latch is shown as following.

## **CONFIGURATION PROGRAMMING FUNCTION**

## **ELANC-PCI Mode Configuration Registers**

#### **MCR**

A mode configuration register(MCR) is used to program the operation mode of the ELANC-PCI. The address is page 0, 0AH. MCR can be updated by software. Reading this register is the same as reading a register in the SLCT core coprocessor. Writing to these registers is done by first reading the register to be written to and then using a slave write operation to update the configurations.

The content of MCR is as following table:

| BIT         | SYMBOL               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|-------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0 1         | PHY0<br>PHY1         | Physical Layer Interface: These two bits select the type of physical interface which the ELANC-PCI attached on. Both the thin Ehternet and thick Ethernet type use the AUI of ELANC-PCI as the input/output interface. The other two UTP types, then, use the TPI of ELANC-PCI as the input/output interface. The output and input pins of AUI or TPI are idle, when the corresponding type is not selected. |  |  |  |  |

|             |                      | PHY1 PHY0 Physical Interface Type  0 0 UTP (with 10BASE-T compatible receive squelch level) 0 1 Thin Ethernet 1 0 Thick Ethernet (AUI port) 1 1 UTP (with reduced receive squelch level)                                                                                                                                                                                                                     |  |  |  |  |

| 2           | GDLNK                | Good Link Status: A read operation on this bit will get the link test status. A "1" indicate that it is link good and a "0" is link fail.  The GDLNK do not imply any information if the PHY0 and PHY1 is programmed as Thin or Thick Ethernet.                                                                                                                                                              |  |  |  |  |

| 3           | LNKEN                | Link Test Pulse enable: The network media auto switching function, link integrity test function and the link test pulse generation function will be enabled when LNKEN = "0". Otherwise, all of these functions will be disabled when LNKEN = "1".                                                                                                                                                           |  |  |  |  |

| 4           | SHLS                 | SRAM High/Low Speed Select:  High speed SRAM with 20nsec access time is selected if SHLS =1. Low speed SRAM with 70nsec access time is selected if SHLS =0.                                                                                                                                                                                                                                                  |  |  |  |  |

| 5<br>6<br>7 | BPS0<br>BPS1<br>BPS2 | BOOT PROM Size: The size of the BOOT PROM is selected by BPS0, BPS1, and BPS2. BPS2 BPS1 BPS0 SIZE 0 0 X No boot PROM 0 1 0 8K 0 1 1 16K 1 0 0 32K 1 0 1 64K 1 1 0 128K 1 1 1 256K                                                                                                                                                                                                                           |  |  |  |  |

## **PCI Bus Operation Configuration Registers**

The W89C940 implement a system configuration registers for PCI bus auto configuration function. The W89C940 support the predefined header portion of the system configuration space (i.e. first 64 bytes of the 256 bytes configuration space). A summarized table for those registers is as following.

| address of    | Register         | Attribute | Default Value  | Write By   |

|---------------|------------------|-----------|----------------|------------|

| configuration | Ü                |           | after power ON | ,          |

| space         |                  |           |                |            |

| 01H~00H       | Vendor-ID        | R/W       | 1050H          | EEPROM     |

| 03H~02H       | Device-ID        | R/W       | 5A5AH          | EEPROM     |

| 05H~04H       | Command          | R/W       | 0000H          | System S/W |

| 07H~06H       | Status           | R/W       | 0280H          | System S/W |

| 08H           | Revision-ID      | R/W       | 00H            | EEPROM     |

| 0BH~09H       | Class-Code       | R         | 020000H        | None       |

| 0CH           | Cache-Line-Size  | R         | 00H            | None       |

| 0DH           | Latency-Timer    | R         | 00H            | None       |

| 0EH           | Header-Type      | R         | 00H            | None       |

| 0FH           | BIST             | R         | 00H            | None       |

| 13H~10H       | I/O-Base-Address | R/W       | FFFFFE1H       | System S/W |

| 17H~14H       | Reserved-Reg0    | R         | H00000000      | None       |

| 1BH~18H       | Reserved-Reg1    | R         | H00000000      | None       |

| 1FH~1CH       | Reserved-Reg2    | R         | H00000000      | None       |

| 23H~20H       | Reserved-Reg3    | R         | H00000000      | None       |

| 27H~24H       | Reserved-Reg4    | R         | H00000000      | None       |

| 2BH~28H       | Reserved-Reg5    | R         | H00000000      | None       |

| 2FH~2CH       | Reserved-Reg6    | R         | H00000000      | None       |

| 33H~30H       | ROM-Base-Address | R/W       | FFFF8001H      | System S/W |

| 37H~34H       | Reserved-Reg7    | R         | H00000000      | None       |

| 3BH~38H       | Reserved-Reg8    | R         | H00000000      | None       |

| 3CH           | Interrupt Line   | R/W       | 00H            | System S/W |

| 3DH           | Interrupt Pin    | R         | 01H            | None       |

| 3EH           | Min-Gnt          | R/W       | 00H            | EEPROM     |

| 3FH           | Max-Lat          | R/W       | 00H            | EEPROM     |

The vendor ID, device ID, revision ID, Min-Gnt and Max-Lat are programmed by EEPROM, i.e. the contents of these register can be updated by EEPROM load only. The I/O base address and the ROM base address registers can be updated by system software. Those system configuration registers should be accessed by a double word access operation. The W89C940 will drive 32 bits data on the bus when these configuration registers are accessed.

#### Vendor ID Register

The vendor I.D. identifies the manufacturer of the device. Valid vendor identifiers are allocated by the PCI SIG to ensure uniqueness. The content of this register will be updated after power on by the EEPROM load operation. The vendor ID should be programmed into the word with 09H address of the EEPROM for power on auto loading.

## Device I.D. Register

The device I.D. identifies the particular device. This identifier is allocated by the vendor. The content of this register will be updated after power on by the EEPROM load operation. The device ID should be programmed into the word with 0AH address of the EEPROM for power on auto loading.

## Command Register

| Bit Location | Attribute | Description                                                                                                                                                                                                                                            |

|--------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0            | R/W       | This bit controls the I/O space access response of W89C940. A value of "0" will disables the W89C940 response. A value of "1" allows the W89C940 to respond to I/O space accesses.                                                                     |

| 1            | R/W       | This bit controls the memory space access response of W89C940. A value of "0" will disables the W89C940 response. A value of "1" allows the W89C940 to respond to memory space accesses.                                                               |

| 2            | R         | The W89C940 do not support PCI bus master function. This bit is fixed to "0".                                                                                                                                                                          |

| 3            | R         | The W89C940 do not support the special cycle operation. This bit is fixed to "0"                                                                                                                                                                       |

| 4            | R         | The W89C940 do not support the memory write cycle and the invalidate command. This bit is fixed to "0".                                                                                                                                                |

| 5            | R         | The W89C940 is not a VGA compatible device. This bit is fixed to "0".                                                                                                                                                                                  |

| 6            | R/W       | This bit controls the parity error response of W89C940. A value of "0" will force the W89C940 ignore a parity error. A value of "1" allows the W89C940 to take a normal action when a parity error is detected. This bit will be reset after power ON. |

| 7            | R         | The W89C940 do not support data stepping function and this bit is fixed to "0" always.                                                                                                                                                                 |

| 8            | -         | This bit is an enable bit for W89C940 internal SERR# driver. A value of "0" will disables the internal SERR# driver. A value of "1" enables the internal SERR# driver.                                                                                 |

| 9~15         | R         | All of these bits are fixed to "0" internally. And no specific function are related to these bits.                                                                                                                                                     |

#### Status Register

| Bit Location | Attribute | Description                                                                                                                                                                                                                                                         |

|--------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15           | R/W       | This bit will be set "1" by W89C940 when it detects a parity error, even if parity error handling is disabled(as controlled by bit 6 in the command register). A "write 1" operation on this bit will clear this bit. This bit will be set "0" after it is cleared. |

| 14           | R/W       | This bit will be set "1" by W89C940 when it assert the internal SERR#. A "write 1" operation on this bit will clear this bit. This bit will be set "0" after it is cleared. This bit is read only for 100 pin package and is fixed to "0".                          |

| 13           | R         | The W89C940 do not support PCI bus master function. This bit is fixed to "0".                                                                                                                                                                                       |

| 12           | R         | The W89C940 do not support PCI bus master function. This bit is fixed to "0".                                                                                                                                                                                       |

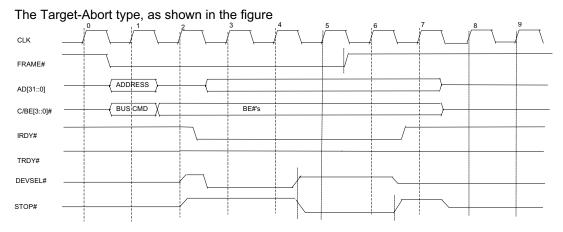

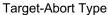

| 11           | R/W       | This bit will be set "1" by W89C940 when it terminates a transaction with target-abort. A "write 1" operation on this bit will clear this bit. This bit will be set "0" after it is cleared.                                                                        |

| 10~9         | R         | The Bit-10 is fixed to "0" and Bit-9 is fixed to "1". It indicated that the W89C940 assert the DEVSEL# with medium speed.                                                                                                                                           |

| 8            | R         | The W89C940 do not support PCI bus master function. This bit is fixed to "0".                                                                                                                                                                                       |

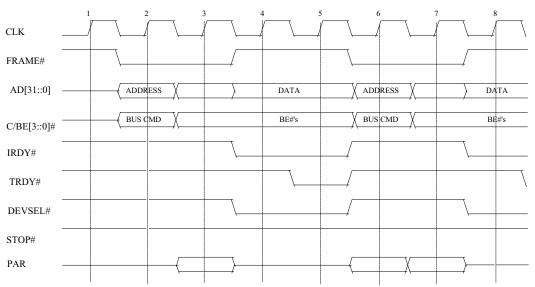

| 7            | R         | The W89C940 support fast back-to-back transaction.                                                                                                                                                                                                                  |

| 6~0          | R         | All of these bits are fixed to "0" internally. And no specific function are related to these bits.                                                                                                                                                                  |

There are two cases that the W89C940 will initiate the target-abort. The first one is the addressing parity check error cause internal SERR# asserted but without STOP# signal and the second one is the byte enable and address check error that the STOP# is asserted. If addressing don't match the following table, the target doesn't transfer the data, but terminate with target abort.

| AD1 | AD0 | C/BE3# | C/BE2# | C/BE1# | C/BE0# |

|-----|-----|--------|--------|--------|--------|

| 0   | 0   | Х      | Х      | Х      | 0      |

| 0   | 1   | Х      | Х      | 0      | 1      |

| 1   | 0   | Х      | 0      | 1      | 1      |

| 1   | 1   | 0      | 1      | 1      | 1      |

## Revision I.D. Register

The revision I.D. is chosen by the vendor. It specifies a device specific revision identifier. Zero is an acceptable value. It can be viewed as a vendor defined extension to the Device I.D. The content of this register will be updated after power on by the EEPROM load operation. The revision ID should be programmed into the 23th byte of the EEPROM for power on auto loading.

#### Class Code Register

The Class Code Register is read only. The code of 020000H indicates that the W89C940 is a Ethernet controller.

#### Cache-Line-Size Register

The W89C940 do not support the Memory Write and Invalidate command. All bits of this register are fixed to "0".

#### Latency-Timer Register

The W89C940 do not implement a writable latency timer. All bits of this register are fixed to "0".

#### Header-Type Register

The W89C940 is a single function device. The bit 7 of header type register is fixed to "0" and all of other bits of this register are also fixed to "0".

## BIST Register

The W89C940 do not support the built in self test function. It will always return "00H" for a reading operation.

#### I/O-Base-Address Register

| Bit           | 31~24 | 23~16 | 15~8 | 7   | 6   | 5   | 4 | 3 | 2 | 1 | 0 |

|---------------|-------|-------|------|-----|-----|-----|---|---|---|---|---|

| Attribute     | R/W   | R/W   | R/W  | R/W | R/W | R/W | R | R | R | R | R |

| Initial Value | FFH   | FFH   | FFH  | 1   | 1   | 1   | 0 | 0 | 0 | 0 | 1 |

The bit 0 fixed to "1" indicates that W89C940 requires the I/O space of the system as its buffer for data transfer. The bit 0 to bit 4 implemented as a read only field imply that W89C940 need a I/O space with a range of 32 bytes. The power-up software can determine how munch address space the device required by writing a value of all 1's to the register and then reading the value back. The W89C940 will return 0's in all don't care address bits(bit 0 ~ bit 4), effectively specifying the address required, if the IDSEL and the configuration command are recognized. The I/O base address will be decided by the bit 5 to bit 31 of the I/O base address register. The system software should write the base address(32 bits address) onto this register. The bit 0 to bit 4 will be ignored by W89C940. The bit 5 to bit 31 will be used as a reference value of the address decoder of the W89C940.

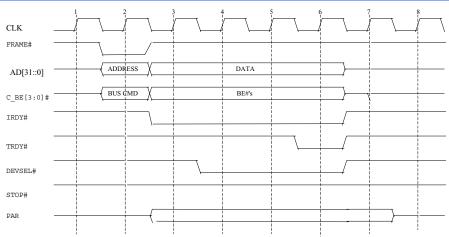

There are nine types of command decoded by C/BE[0:3]# during the address phase of a transaction. These nine types of command are as the following table.

| C/BE[3:0]# | Command Type                                                                          |

|------------|---------------------------------------------------------------------------------------|

| 0010       | I/O Read                                                                              |

| 0011       | I/O Write                                                                             |

| 0110       | Memory Read                                                                           |

| 0111       | Memory Write                                                                          |

| 1010       | Configuration Read                                                                    |

| 1011       | Configuration Write                                                                   |

| 1100       | Memory Read Multiple, this command will be decoded as the Memory Read command         |

| 1110       | Memory Read Line, this command will be decoded as the Memory Read command             |

| 1111       | Memory Write and Invalidate, this command will be decoded as the Memory Write command |

The last three commands are used in cache memory access. The application of W89C940 do not support this command.

#### ROM-Base-Address Register

| Bit           | 31~24 | 23~16 | 15~8 | 7~0 |

|---------------|-------|-------|------|-----|

| Attribute     | R/W   | R/W   | R/W  | R/W |

| Initial Value | FFH   | FFH   | 80H  | 01H |

The W89C940 supports 8Kx8, 16Kx8, 32Kx8, 64Kx8, 128Kx8 and 256Kx8 ROM address decoding function. For a 8Kx8 ROM application, the upper 19 bits of this register correspond to the upper 19 bits of the expansion ROM base address. The lower 13 bits of this register correspond to the size of the expansion ROM. Those bits correspond to the size of the expansion ROM are determined by MCR bit 5, bit 6 and bit 7 and can not be writable by the system configuration write command. The device independent configuration software can only determined the bits corresponding to the base address. The following table describe the relationship between the addressing bus, sizing bits and the MCR bit 5/6/7.

| MCR.7 | MCR.6 | MCR.5 | Addressing Bits | Sizing Bits | ROM Size    |

|-------|-------|-------|-----------------|-------------|-------------|

| 0     | 0     | Χ     | None            | None        | No BOOT ROM |

| 0     | 1     | 0     | 31~13           | 12~0        | 8Kx8        |

| 0     | 1     | 1     | 31~14           | 13~0        | 16Kx8       |

| 1     | 0     | 0     | 31~15           | 14~0        | 32Kx8       |

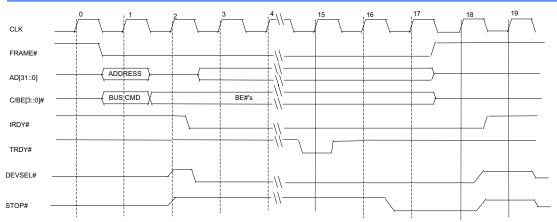

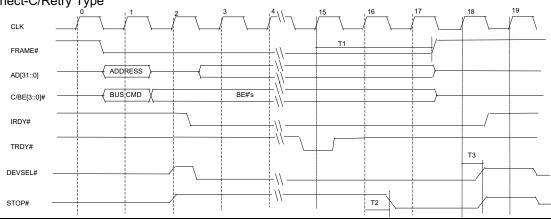

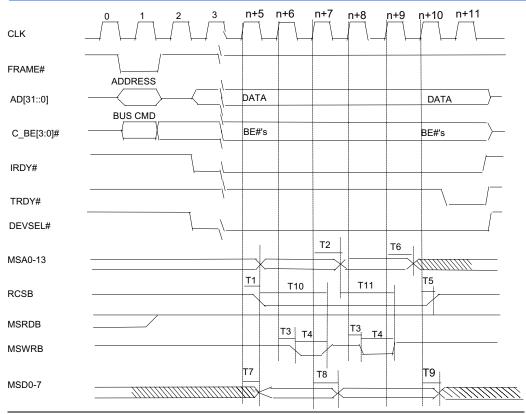

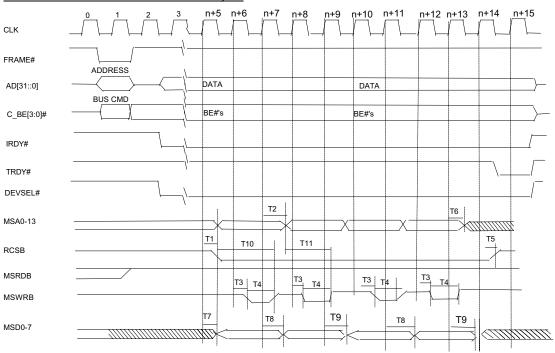

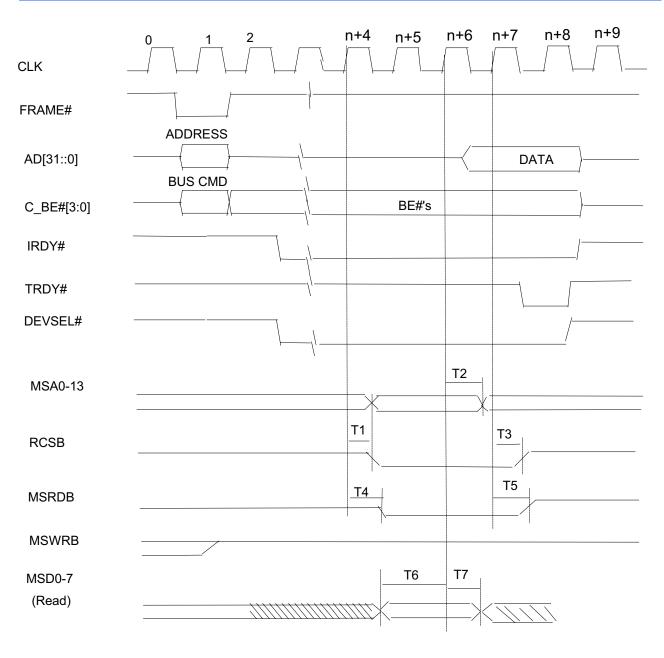

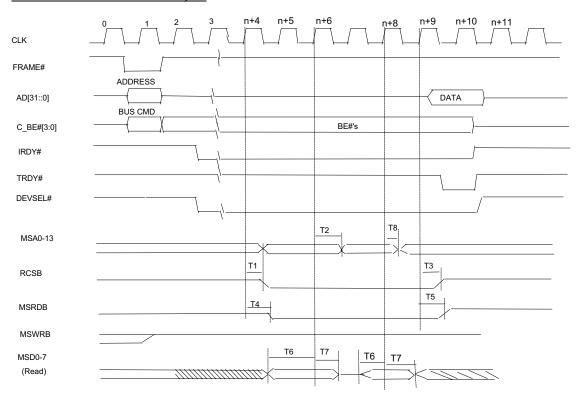

| 1     | 0     | 1     | 31~16           | 15~0        | 64Kx8       |